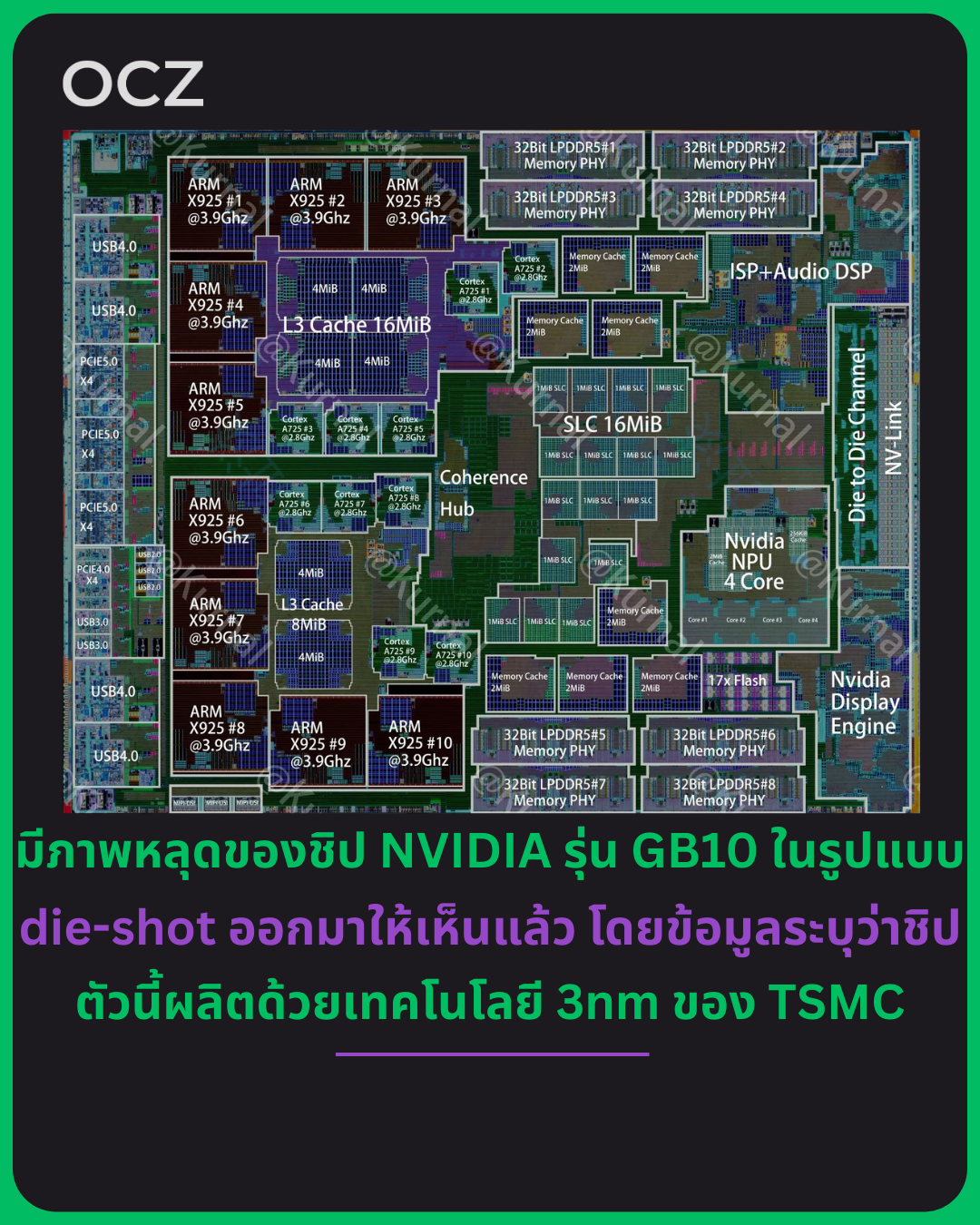

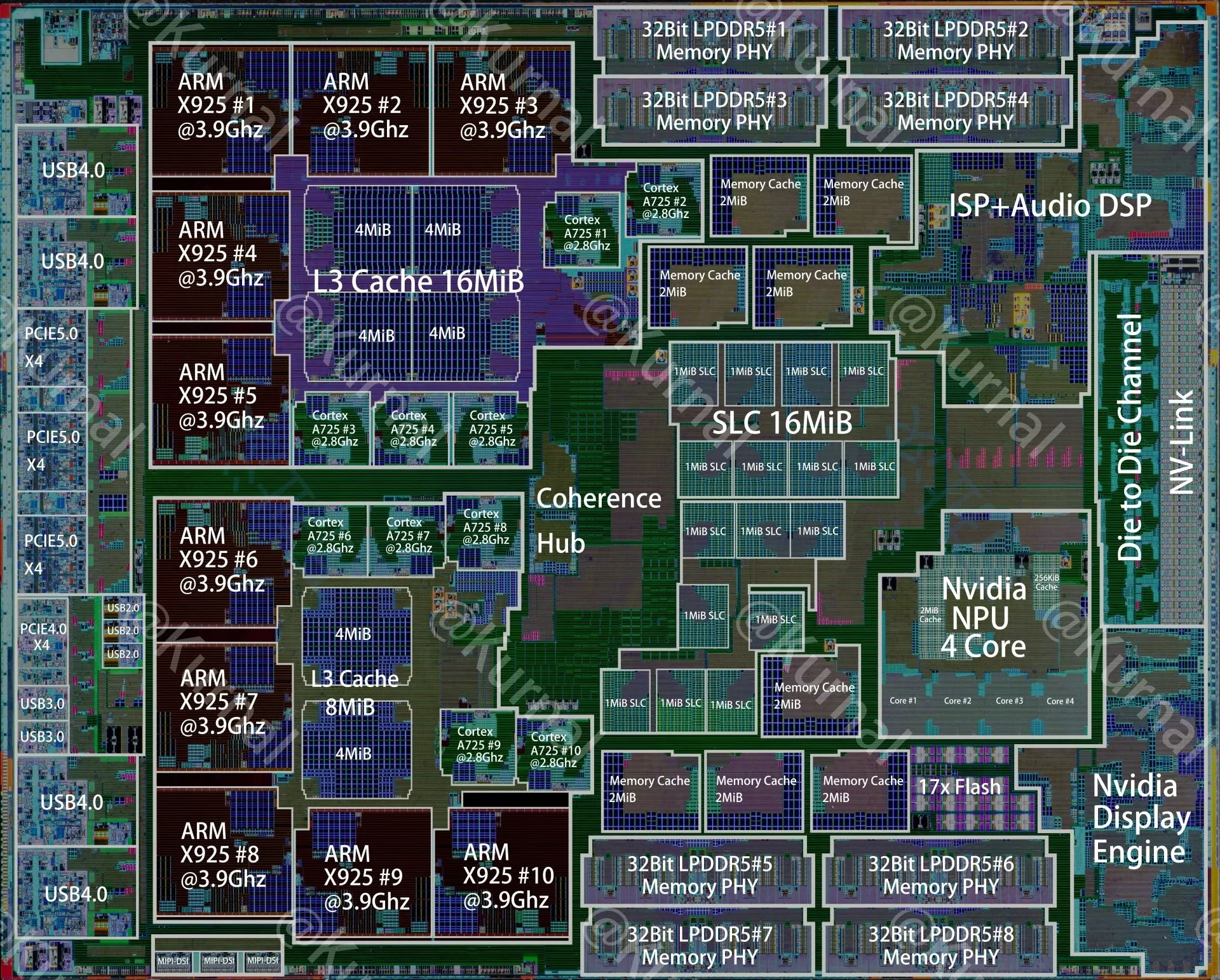

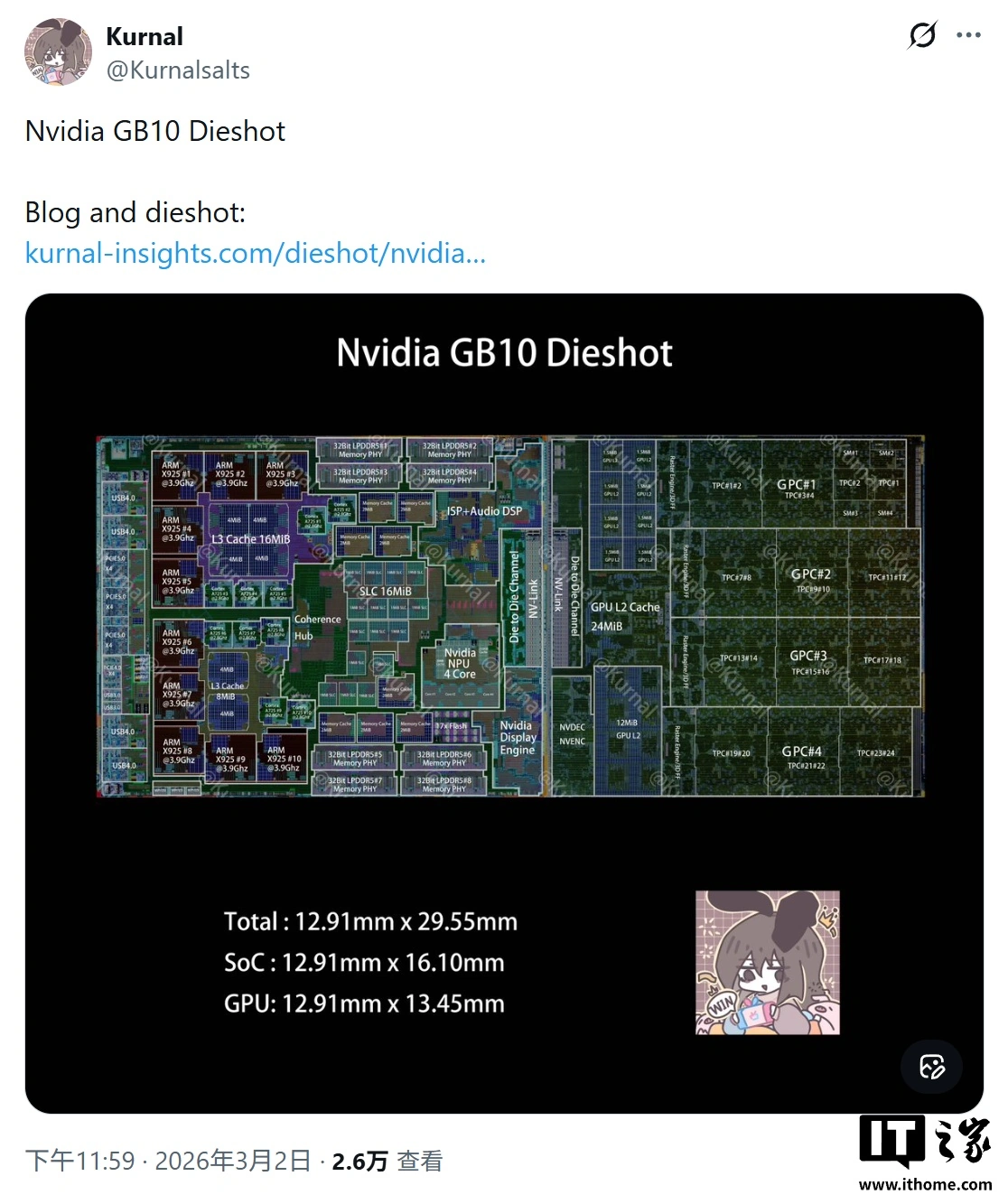

โพสต์บนแพลตฟอร์ม X เมื่อวันที่ 4 มีนาคมที่ผ่านมา เผยภาพ die-shot ของชิป NVIDIA GB10 พร้อมคำอธิบายประกอบอย่างละเอียด

Die-shot คือภาพถ่ายระดับจุลทรรศน์หรือผังโครงสร้างภายในของชิป ใช้สำหรับวิเคราะห์การออกแบบ การจัดวางบล็อกต่าง ๆ และขนาดพื้นที่ของแต่ละส่วนบนแผ่นซิลิคอน

ชิป NVIDIA GB10 เป็นผลงานพัฒนาร่วมกันระหว่าง MediaTek และ NVIDIA โดย MediaTek รับผิดชอบส่วนซีพียู ส่วน NVIDIA พัฒนาในฝั่งจีพียู

จุดที่น่าสนใจคือ GB10 ใช้กระบวนการผลิต N3 (3 นาโนเมตร) ของ TSMC ขณะที่จีพียู Blackwell รุ่นอื่น ๆ ของ NVIDIA ที่มีอยู่ในตลาด เช่น AI accelerator และการ์ดจอ GeForce ส่วนใหญ่ยังใช้กระบวนการผลิต 5 นาโนเมตรแบบปรับแต่งพิเศษ (4N)

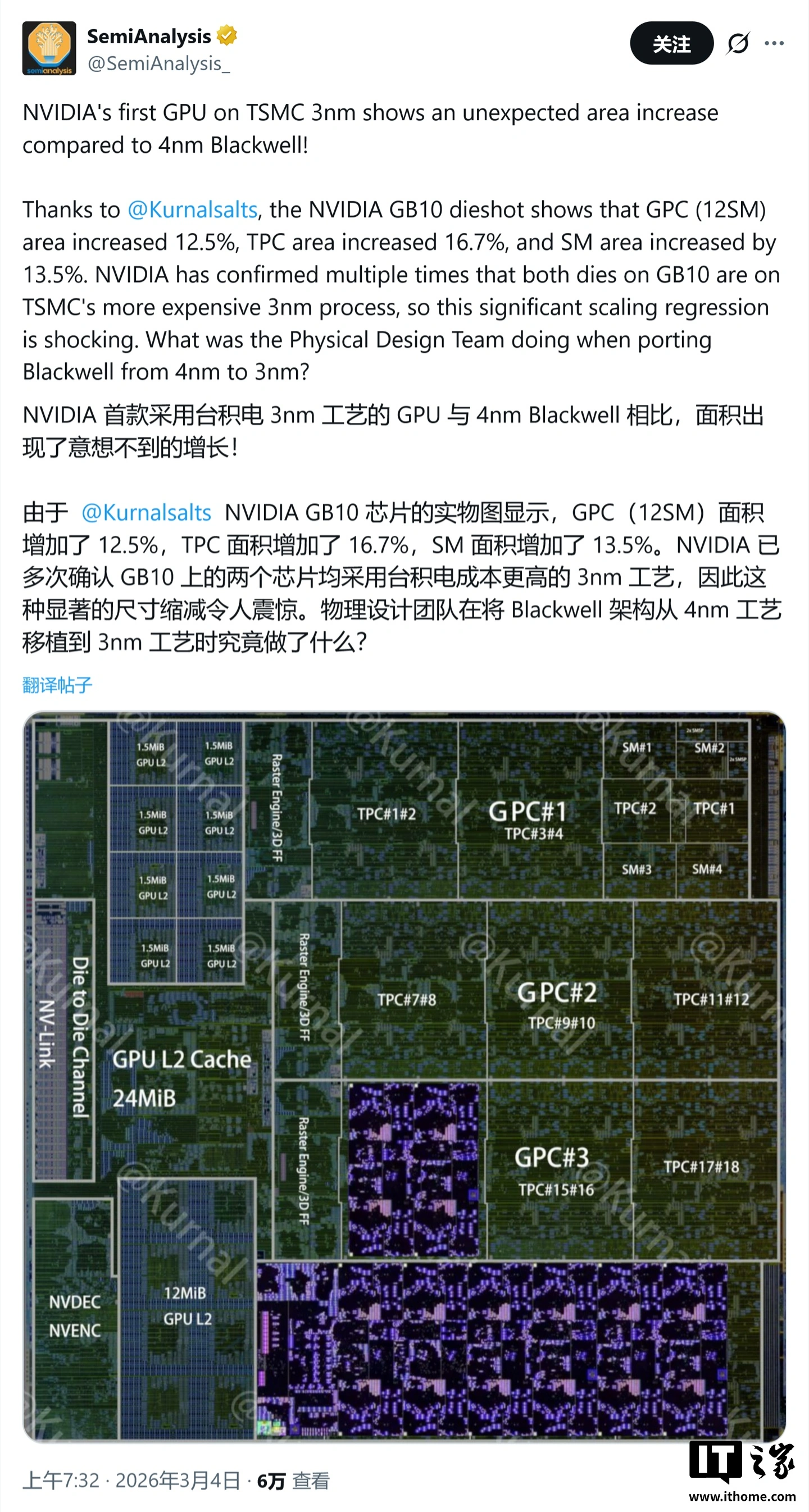

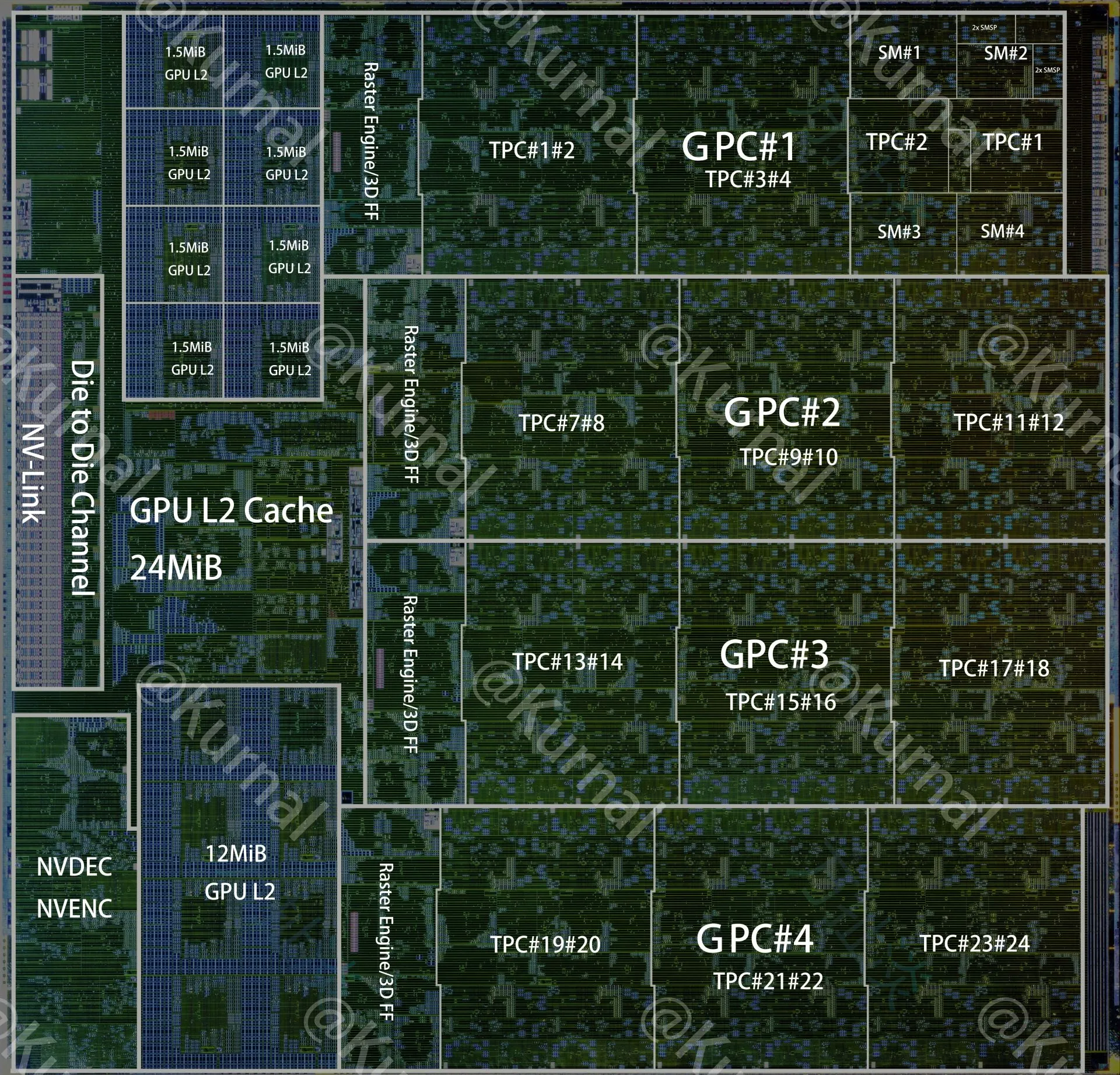

อย่างไรก็ตาม การวิเคราะห์เปรียบเทียบพบประเด็นที่ดูสวนทางกับความคาดหวัง นั่นคือ พื้นที่ของบางบล็อกในจีพียู Blackwell ภายใน GB10 กลับมีขนาดใหญ่กว่าเวอร์ชัน 5 นาโนเมตรที่รู้จักกันก่อนหน้านี้

รายละเอียดขนาดชิป:

-

ขนาดชิปรวมของ GB10: 12.91 x 29.55 มม.

-

ขนาดส่วนจีพียู: 12.91 x 13.45 มม.

เมื่อเทียบกับรุ่น 5 นาโนเมตร:

-

พื้นที่ GPC (Graphics Processing Cluster) เพิ่มขึ้น 12.5%

-

พื้นที่ TPC (Texture Processing Cluster) เพิ่มขึ้น 16.7%

-

พื้นที่ SM (Streaming Multiprocessor) เพิ่มขึ้น 13.5%

ตามทฤษฎีแล้ว กระบวนการผลิตที่ล้ำหน้ากว่าอย่าง 3 นาโนเมตรควรช่วยลดขนาดโครงสร้างได้ แล้วเหตุใดพื้นที่จึงขยายขึ้น?

นักวิเคราะห์คาดว่า ทีมออกแบบด้านกายภาพ (physical design team) อาจใช้แนวทาง “เผื่อระยะ” หรือออกแบบแบบผ่อนปรน (lenient design) ระหว่างการย้ายกระบวนการผลิต (process migration) เพื่อเพิ่มอัตราผลผลิต (yield) ในช่วงต้นของการใช้โหนดใหม่ ซึ่งเป็นแนวทางที่พบได้บ่อยในช่วงเริ่มต้นของเทคโนโลยีการผลิตใหม่

อีกปัจจัยหนึ่งคือ GB10 ใช้สถาปัตยกรรม SM 12.1 ซึ่งแตกต่างจาก SM 10.0/10.3 ที่ใช้ใน B100 และ B200 ทำให้ข้อกำหนดด้านความเข้ากันได้ (compatibility) อาจมีผลต่อการจัดวางเลย์เอาต์ของวงจร

นอกจากนี้ยังมีความเป็นไปได้ว่าการออกแบบที่ “เผื่อพื้นที่” มากขึ้น อาจช่วยรองรับความถี่สัญญาณนาฬิกาที่สูงกว่า โดย B200 มี boost clock ที่ 2.1 GHz ขณะที่ GB10 มี boost clock ประมาณ 2.5 GHz ความแตกต่างด้านความถี่ รวมถึงข้อกำหนดด้านการระบายความร้อน อาจเป็นปัจจัยสำคัญที่ทำให้เลย์เอาต์วงจรเปลี่ยนไป

ที่มา: IT Home