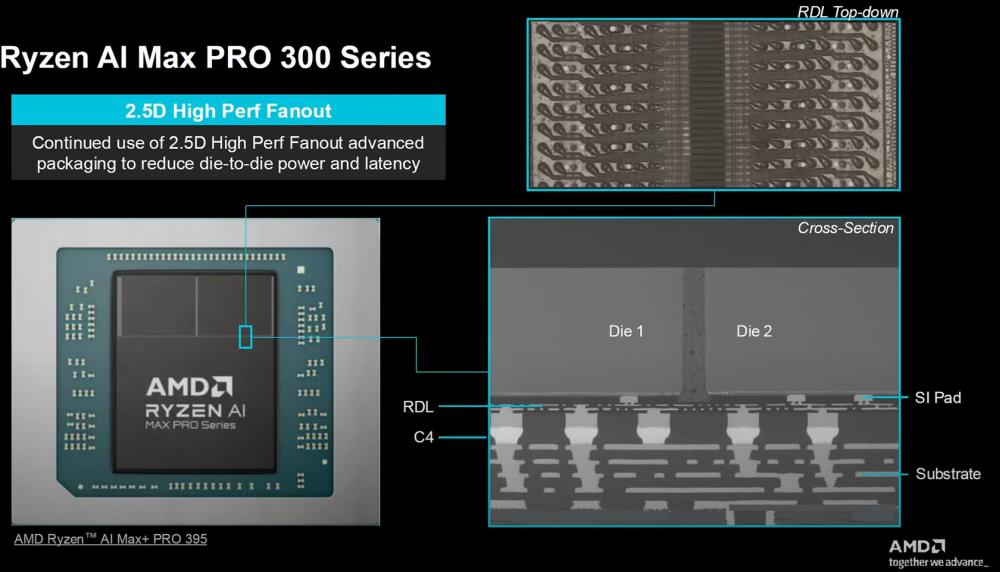

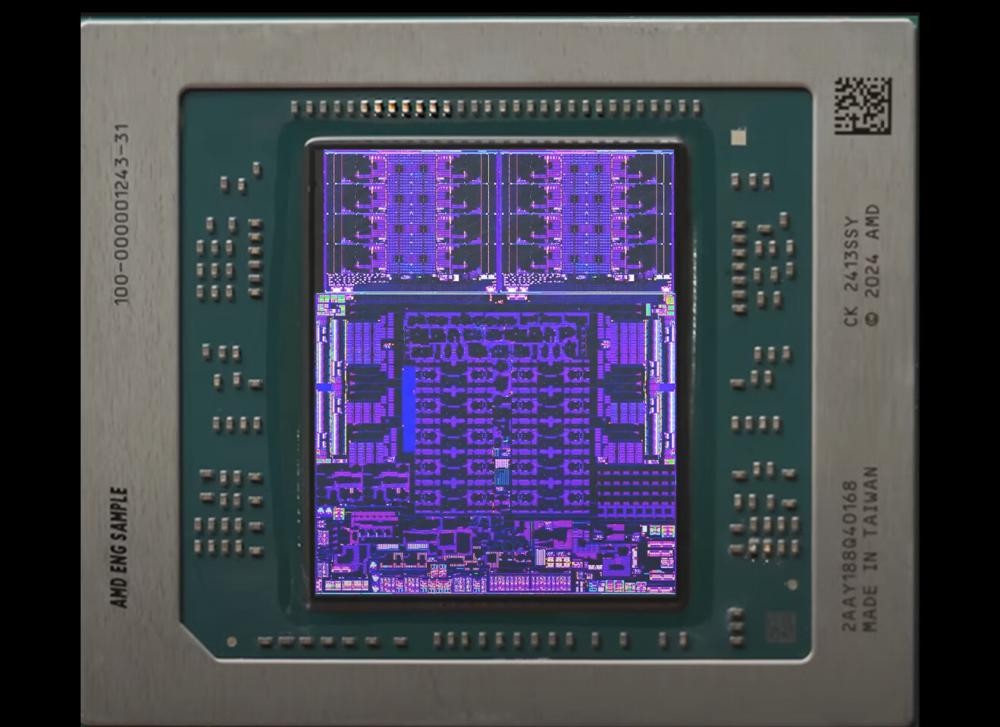

อ้างอิงจากช่อง High Yield บน YouTube มีรายงานว่า AMD กำลังเดินห่างออกจากการเชื่อมต่อ die-to-die (D2D) แบบ SERDES ที่เคยใช้ และหันมาใช้การเชื่อมต่อแบบขนานกว้าง หรือที่เรียกว่า “sea-of-wires” ซึ่งเดินสายผ่านแพ็กเกจ fan-out และ RDL packaging โดยมีสัญญาณแรก ๆ ของการเปลี่ยนแปลงนี้ปรากฏให้เห็นในภาพหลุดของ Strix Halo APU

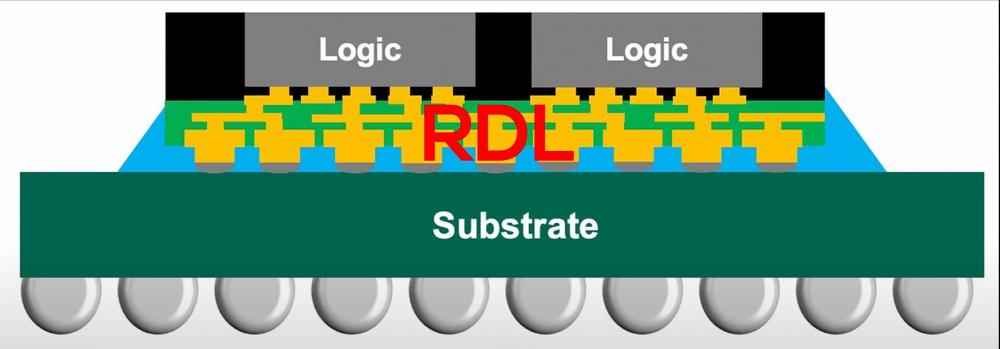

จากตัวอย่างที่หลุดออกมา จะเห็นว่ามี rectangular pad field (แผงขั้วสี่เหลี่ยม) ตรงตำแหน่งที่คาดว่าจะเป็น fan-out และ บล็อก SERDES ขนาดใหญ่ที่เคยอยู่ขอบ CCD ก็หายไป รูปแบบนี้เมื่อรวมกับทางเลือกการแพ็กเกจที่สอดคล้องกับ TSMC InFO-oS ทำให้คาดการณ์ได้ว่า AMD กำลังทดลองใช้ การเดินสัญญาณแบบขนานหนาแน่น เพื่อให้ fabric lanes วิ่งข้ามแพ็กเกจโดยตรง โดยไม่ต้องถูกบีบรวมเป็นลิงก์ serial ความเร็วสูงไม่กี่เส้นเหมือนแต่ก่อน

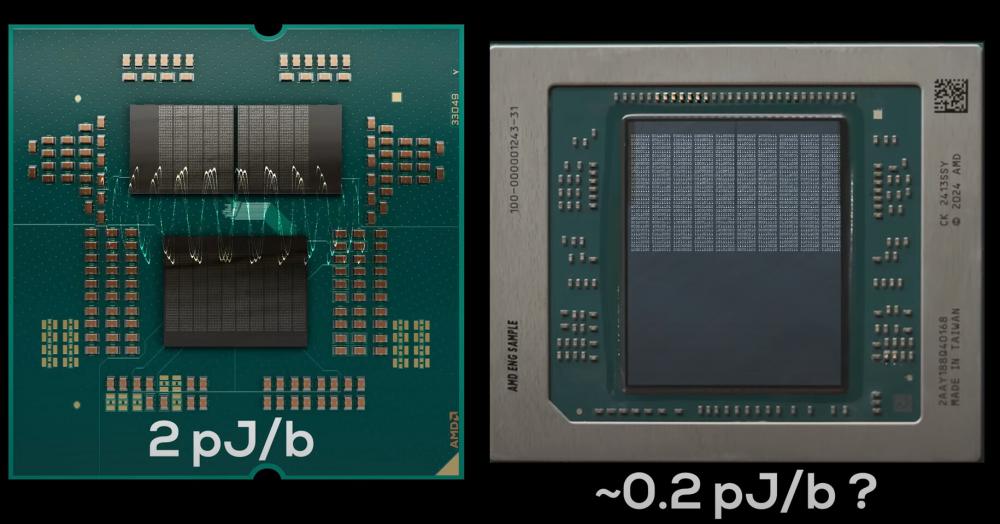

การเชื่อมต่อแบบ serial ปกติจำเป็นต้องมีขั้นตอน serialize/deserialize ที่ขอบแพ็กเกจทุกครั้ง ซึ่งกินพลังงานและเพิ่ม latency เนื่องจากต้องทำ clock recovery, equalization รวมถึง encoding/decoding แต่การย้ายมาใช้ เส้นสัญญาณขนานสั้น ๆ จำนวนมาก จะช่วยตัดภาระของ PHY เหล่านี้ออกไป ลดดีเลย์รอบการสื่อสาร และสามารถขยายแบนด์วิธได้ง่าย ๆ เพียงเพิ่มจำนวน lanes ทางกายภาพ อีกทั้งยังช่วยคืนพื้นที่ที่เดิมต้องใช้กับบล็อก SERDES ขนาดใหญ่ ทำให้ CCD, memory controller และ accelerator สามารถจัดวางใกล้กันมากขึ้น พร้อมลดต้นทุนการสื่อสารในตัว

อย่างไรก็ตาม วิธีนี้ก็มีข้อท้าทายจริง ๆ เพราะการอัดสายสัญญาณขนานจำนวนมากไว้ใต้ได้นั้นต้องเจอกับปัญหา signal integrity, ความร้อน, การเดินสาย และข้อจำกัดด้านการผลิต ทำให้จำเป็นต้องออกแบบ multi-layer RDL และทำงานร่วมกันอย่างใกล้ชิดระหว่างทีมไดกับทีมแพ็กเกจ หาก AMD สามารถแก้โจทย์เหล่านี้ได้และนำแนวทางดังกล่าวมาใช้กับ Zen 6 ก็อาจทำให้ซีพียูรุ่นใหม่มีประสิทธิภาพต่อวัตต์ที่ดีขึ้น ลด latency ลงได้จริง และแม้แต่ IMC (memory controller) ก็อาจเร็วขึ้นเพราะดีเลย์จาก I/O die ลดลงด้วย

ที่มา : TechPowerUp