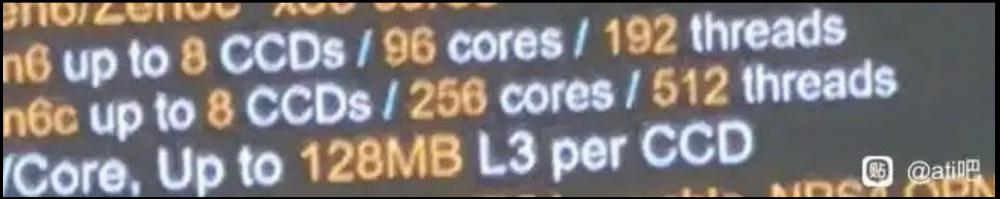

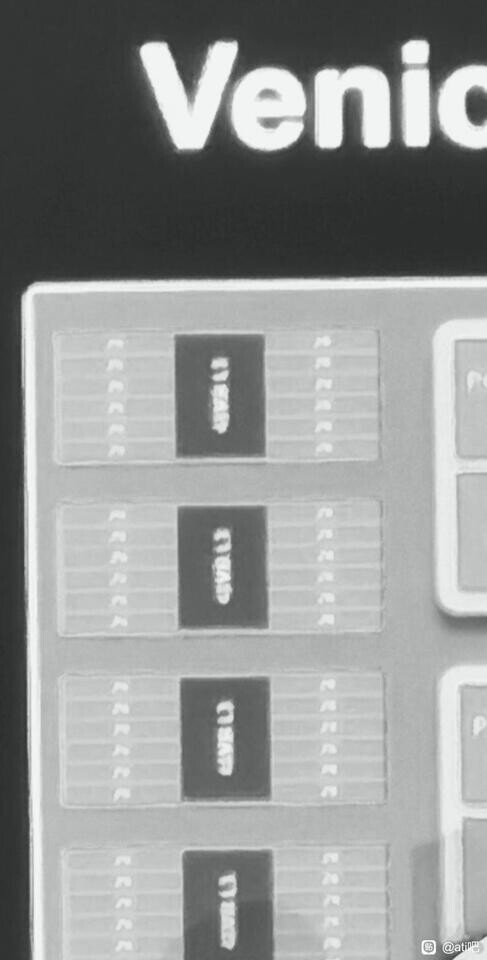

AMD กำลังเตรียมกำหนดมาตรฐานประสิทธิภาพศูนย์ข้อมูลใหม่ด้วยโปรเซสเซอร์ EPYC "Venice" รุ่นที่ 6 ที่กำลังจะมาถึง ซึ่งสร้างขึ้นจากการออกแบบคอร์ "Zen 6" และ "Zen 6C" ล่าสุด และโหนดระดับ 2 นาโนเมตรตัวแรกจาก TSMC แผนภาพที่หลุดมาและรายงานฟอรัมระบุว่า Venice จะนำเสนอความสามารถในการปรับขนาดคอร์เพิ่มเติม ความจุหน่วยความจำ และประสิทธิภาพแคชสำหรับเวิร์กโหลดเซิร์ฟเวอร์ที่ต้องการประสิทธิภาพสูง ที่ใจกลางของแพลตฟอร์ม Venice คือการออกแบบโมดูลชิปหลายตัวที่มี Core Complex Die (CCD) สูงสุด 8 ตัวที่จัดเรียงรอบ Central I/O Die (IOD) หนึ่งตัวหรือมากกว่านั้น ในการกำหนดค่า Zen 6 นั้น CCD แต่ละตัวจะมีคอร์ "แบบคลาสสิก" 12 คอร์ ซึ่งให้คอร์สูงสุด 96 คอร์และ 192 เธรดต่อซ็อกเก็ต มีข่าวลือว่าแคชต่อ CCD หนึ่งตัวจะมีขนาด 128 MB ของ L3 ที่ใช้ร่วมกัน ซึ่งเป็นสองเท่าของรุ่นก่อนหน้า โดยให้แคช L3 สูงสุด 1 TB ในแพ็คเกจแปด CCD ที่บรรจุข้อมูลครบถ้วน สำหรับลูกค้าที่ให้ความสำคัญกับจำนวนเธรดดิบมากกว่าประสิทธิภาพต่อคอร์ รุ่น Zen 6C จะขยายขอบเขตเป็น 256 คอร์ "หนาแน่น" และ 512 เธรดด้วยการใช้การออกแบบคอร์ที่เบากว่าและจำนวน CCD ที่สูงขึ้น แม้จะมีความหนาแน่นเพิ่มขึ้น แต่แต่ละคอร์ของ Zen 6C ยังคงรักษาแคช L3 ไว้ 2 MB ซึ่งรักษาข้อดีของเวลาแฝงไว้แม้ในระดับขนาดใหญ่ แบนด์วิดท์หน่วยความจำยังได้รับการยกระดับอย่างมาก: Venice จะรองรับการกำหนดค่า DDR5 ทั้งแบบ 16 ช่องสัญญาณ (SP7) และ 12 ช่องสัญญาณ (SP8) รองรับ RAM ระบบสูงสุด 6 TB ต่อซ็อกเก็ต จำนวนเลน PCIe Gen 5 ยังคงไม่ทราบแน่ชัด แต่คาดว่าจะมากกว่า 128 เลน ซึ่งเป็นจำนวนเดียวกับซีพียู EPYC รุ่นที่ 5 ในอดีต เป้าหมายด้านความร้อนและพลังงานทำให้ซ็อกเก็ตทั้งสองแตกต่างกัน โดยคาดว่ารุ่น SP7 จะมี TDP ประมาณ 600 W เพิ่มขึ้นจาก 400 W ในชิป Zen 5 ในปัจจุบัน ขณะที่ชิ้นส่วน SP8 ตั้งเป้าไว้ที่ 350-400 W เพื่อให้เหมาะกับแร็คที่มีความหนาแน่นปานกลางมากขึ้น แนวทางแบบแบ่งระดับนี้จะช่วยให้ไฮเปอร์สเกลเลอร์และลูกค้าองค์กรสามารถสร้างสมดุลระหว่างประสิทธิภาพ ประสิทธิผล และโครงสร้างพื้นฐานด้านการระบายความร้อน โดยเฉพาะอย่างยิ่งในระดับที่ไฮเปอร์สเกลเลอร์มี วันเปิดตัวที่คาดการณ์ไว้คือช่วงปลายปี 2025 หรือต้นปี 2026

ที่มา : TechPowerUp