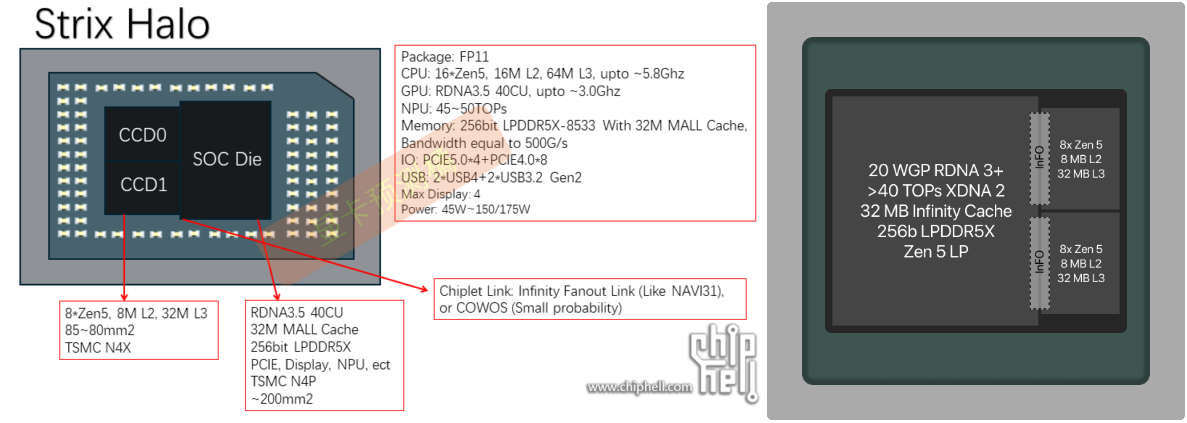

เห็นได้ชัดว่าโปรเซสเซอร์ AMD "Strix Halo" เป็นของจริงและมีขนาดใหญ่ ชิปนี้ได้รับการออกแบบมาให้เหนือกว่า Apple M3 Pro และ M3 Max โดยให้โน้ตบุ๊กพกพาสะดวกมีประสิทธิภาพกราฟิกที่ทรงพลัง โปรเซสเซอร์ที่ใช้ชิปเล็ต ไม่ต่างจากซ็อกเก็ตเดสก์ท็อป "Raphael" และ "Dragon Range" BGA แบบเคลื่อนที่ โปรเซสเซอร์ "Strix Halo" ประกอบด้วย CCD หนึ่งหรือสองตัวที่มีแกน CPU ซึ่งต่อเข้ากับแม่พิมพ์ขนาดใหญ่ ซึ่งในทางเทคนิคแล้วคือ cIOD ( I/O ไคลเอ็นต์ตาย) แต่มี iGPU ขนาดใหญ่และ NPU ประเด็นเบื้องหลัง "Strix Halo" คือการลดความจำเป็นในการใช้ GPU แยกตามกลุ่มประสิทธิภาพ และอนุรักษ์พื้นที่ PCB ของมัน

ตามการรั่วไหลของ Harukaze5719 ซึ่งเป็นแหล่งที่เชื่อถือได้สำหรับการรั่วไหลของ AMD "Strix Halo" มาในแพ็คเกจ BGA ที่มีชื่อว่า FP11 ซึ่งมีขนาด 37.5 mm x 45 mm ซึ่งใหญ่กว่าขนาด 25 mm x 40 mm ของแพ็คเกจ FP8 BGA อย่างเห็นได้ชัด โปรเซสเซอร์มือถือ "Strix Point", "Hawk Point" และ "Phoenix" ปกติถูกสร้างขึ้น มีขนาดใหญ่กว่าแพ็คเกจ FL1 BGA ขนาด 40 มม. x 40 มม. ของ "Dragon Range" และโปรเซสเซอร์โน้ตบุ๊กสำหรับเล่นเกม "Fire Range" ที่กำลังจะเปิดตัวเร็วๆ นี้ "Strix Halo" นำเสนอ CCD แบบ 4 nm "Zen 5" แบบเดียวกันหนึ่งหรือสองตัวบนเดสก์ท็อป "Granite Ridge" และโปรเซสเซอร์มือถือ "Fire Range" แต่เชื่อมต่อกับ I/O die ที่ใหญ่กว่ามากดังที่เราได้กล่าวไปแล้ว

ณ จุดนี้ ยังไม่ทราบโหนดโรงหล่อของ I/O die ของ "Strix Halo" แต่ไม่น่าจะน่าจะเป็นโหนด 6 nm เดียวกันกับ cIOD ที่ AMD ใช้กับโปรเซสเซอร์ไคลเอนต์อื่นที่ใช้ "Zen 4 " และ "เซน 5" คงไม่น่าแปลกใจหาก AMD ใช้โหนด 4 nm แบบเดียวกับที่ใช้กับ "Phoenix" สำหรับ I/O die นี้ เหตุผลหลักที่โหนดขั้นสูงได้รับการรับประกันก็เนื่องมาจาก iGPU ขนาดใหญ่ ซึ่งมีโปรเซสเซอร์เวิร์กกรุ๊ป (WGP) จำนวน 20 ตัว หรือหน่วยประมวลผล (CU) 40 หน่วย มูลค่าตัวประมวลผลสตรีม 2,560 ตัว ตัวเร่งความเร็ว AI 80 ตัว และตัวเร่งความเร็ว Ray 40 ตัว iGPU นี้ใช้สถาปัตยกรรมกราฟิก RDNA 3.5 ล่าสุด

สำหรับมุมมอง iGPU ของโปรเซสเซอร์ 4 นาโนเมตร "Strix Point" ปกติมี 8 WGP (16 CU, 1,024 สตรีมโปรเซสเซอร์) แล้วก็มี NPU AMD คาดว่าจะพกพา XDNA 2 NPU ที่รองรับ TOPS 50 TOPS แบบเดียวกับที่ใช้ใน "Strix Point" ปกติบน I/O die ของ "Strix Halo" ทำให้โปรเซสเซอร์มีความสามารถ Microsoft Copilot+

อินเทอร์เฟซหน่วยความจำของ "Strix Halo" ถือเป็นปริศนามานานแล้ว ลอจิกบอกว่าการมีคอร์ CPU "Zen 5" 16 คอร์และ GPU หน่วยประมวลผล 40 คอร์ที่ใช้ร่วมกันแม้กระทั่งอินเทอร์เฟซหน่วยความจำ DDR5 แบบดูอัลแชนเนลปกติด้วยความเร็วสูงสุดเท่าที่เป็นไปได้เป็นความคิดที่ไม่ดี เนื่องจากทั้ง CPU และ iGPU จะใช้แบนด์วิดท์ที่รุนแรง หิวโหย นอกจากนี้ยังมี NPU ที่ต้องพิจารณาด้วย เนื่องจากการประมวลผลแบบ AI เป็นแอปพลิเคชันที่ไวต่อหน่วยความจำ

เรามีทฤษฎีที่นอกเหนือจากอินเทอร์เฟซ LPDDR5X สำหรับคอร์ CPU แล้ว แพ็คเกจ "Strix Halo" ยังมีการเดินสายสำหรับหน่วยความจำ GDDR6 แบบแยก แม้แต่อินเทอร์เฟซหน่วยความจำ GDDR6 128 บิตที่ค่อนข้างแคบที่ทำงานที่ 20 Gbps ก็ยังให้แบนด์วิธหน่วยความจำ iGPU 320 GB/s ซึ่งเพียงพอสำหรับกราฟิกตามส่วนประสิทธิภาพ นี่หมายความว่านอกจากชิป LPDDR5X แล้ว ก็จะมีชิป GDDR6 สี่ตัวบน PCB iGPU ยังมีหน่วยความจำแคช Infinity Cache on-die ขนาด 32 MB ซึ่งดูเหมือนว่าจะเห็นด้วยกับทฤษฎีของเราเกี่ยวกับอินเทอร์เฟซ GDDR6 128 บิตสำหรับ iGPU โดยเฉพาะ

ที่มา : TechPowerUp

ที่มา : TechPowerUp