เมื่อเดือนมกราคมที่ผ่านมา เราได้รายงานเกี่ยวกับ AMD ที่ออกแบบ CCD "Zen 6" รุ่นถัดไปบนโหนดขนาด 3 นาโนเมตรโดย TSMC และพัฒนาไดย์ I/O เซิร์ฟเวอร์และไคลเอนต์รุ่นใหม่ (cIOD และ sIOD) ไดย์ I/O เป็นชิ้นส่วนซิลิกอนที่สำคัญที่ประกอบด้วยส่วนประกอบที่ไม่ใช่แกนหลักของโปรเซสเซอร์ทั้งหมด รวมถึงตัวควบคุมหน่วยความจำ คอมเพล็กซ์รูท PCIe และอินเทอร์คอนเนกต์ Infinity Fabric ไปยัง CCD และการเชื่อมต่อแบบหลายซ็อกเก็ต เมื่อตอนนั้น มีรายงานว่าไดย์ I/O รุ่นใหม่เหล่านี้ได้รับการออกแบบบนกระบวนการผลิตซิลิกอนขนาด 4 นาโนเมตร ซึ่งตีความว่าเป็นโหนดขนาด 4 นาโนเมตรที่ AMD ชื่นชอบ นั่นคือ TSMC N4P ซึ่งบริษัทใช้สร้างทุกอย่างตั้งแต่โปรเซสเซอร์มือถือ "Strix Point" ในปัจจุบันไปจนถึง CCD "Zen 5" ปรากฏว่า AMD มีแผนอื่น และกำลังสำรวจโหนดขนาด 4 นาโนเมตรโดย Samsung

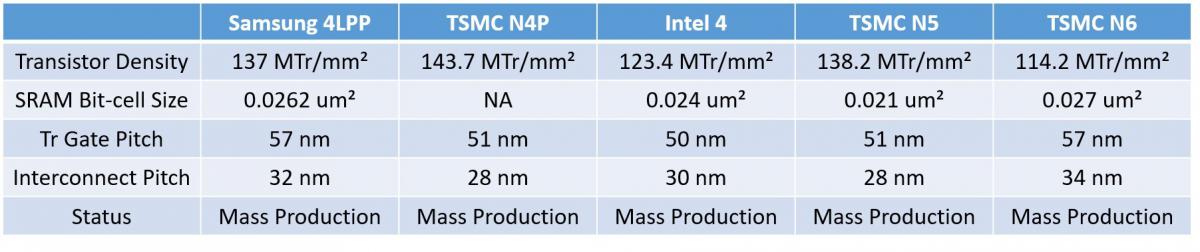

โหนดนี้มีแนวโน้มสูงที่จะเป็น Samsung 4LPP หรือที่รู้จักกันในชื่อ SF4 ซึ่งผลิตเป็นจำนวนมากตั้งแต่ปี 2022 ตารางด้านล่างแสดงให้เห็นว่า SF4 เปรียบเทียบกับ TSMC N4P และ Intel 4 ได้อย่างไร โดยจะแสดงให้เห็นว่ามีความสมดุลระหว่างทั้งสองอย่าง นอกจากนี้ เรายังได้เพิ่มค่าสำหรับโหนด TSMC N5 ซึ่งเป็นแหล่งที่มาของ N4P และคุณจะเห็นได้ว่า SF4 มีความหนาแน่นของทรานซิสเตอร์ที่เทียบเคียงได้กับ N5 และมีการปรับปรุงความหนาแน่นของทรานซิสเตอร์อย่างมีนัยสำคัญเมื่อเทียบกับ TSMC N6 ซึ่ง AMD ใช้สำหรับ sIOD และ cIOD รุ่นปัจจุบัน โหนด 4 นาโนเมตรใหม่จะช่วยให้ AMD ลด TDP ของไดย์ I/O นำโซลูชันการจัดการพลังงานใหม่มาใช้ และที่สำคัญกว่านั้น ความจำเป็นในการใช้ไดย์ I/O ใหม่เกิดจากความจำเป็นในการอัปเดตตัวควบคุมหน่วยความจำที่รองรับความเร็ว DDR5 ที่สูงขึ้นและความเข้ากันได้กับ DIMM ประเภทใหม่ เช่น CUDIMM, RDIMM ที่มี RCD เป็นต้น

ที่มา : TechPowerUp

ที่มา : TechPowerUp