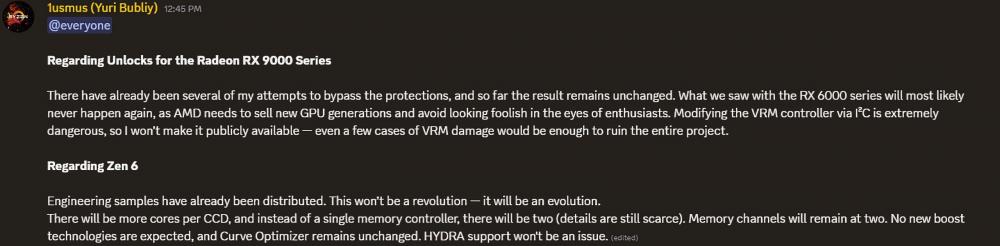

มีรายงานว่า AMD กำลังทดสอบโปรเซสเซอร์เดสก์ท็อป Ryzen รุ่นต่อไปด้วยสถาปัตยกรรมไมโคร "Zen 6" ซึ่งมีชื่อรหัสว่า "Medusa Ridge" เพื่อปิดฉากพันธมิตร เช่น นักออกแบบแพลตฟอร์มและผู้ผลิตอุปกรณ์ดั้งเดิม (OEM) Yuri Bubliy หรือที่รู้จักในชื่อ 1usmus ผู้เขียนซอฟต์แวร์ปรับแต่ง Hydra และเครื่องคิดเลข DRAM สำหรับ Ryzen ซึ่งปัจจุบันได้เลิกใช้งานแล้ว กล่าว AMD ได้ทำการอัปเดตทั้ง CCD และไดย์ I/O ของไคลเอนต์ AMD ยืนยันว่ากำลังสร้าง CCD "Zen 6" บนโหนด TSMC N2 (2 นาโนเมตร) ซึ่งเข้าสู่การผลิตแบบเสี่ยงภัยเมื่อต้นปีนี้ คาดว่าโหนดนี้จะพร้อมสำหรับการผลิตชิป 2 นาโนเมตรจำนวนมากภายในปีนี้ โหนด 2 นาโนเมตรนี้แสดงให้เห็นถึงความหนาแน่นของทรานซิสเตอร์ที่เพิ่มขึ้นอย่างมากจากโหนด TSMC N4P ปัจจุบันที่ AMD ใช้สร้าง CCD "Zen 5" แบบ 8 คอร์ ซึ่ง 1usmus และแหล่งข้อมูลอื่นๆ ระบุว่า AMD จะใช้โหนดนี้เพื่อเพิ่มจำนวนคอร์ CPU ต่อ CCD

แหล่งข่าวชี้ให้เห็นถึงความเป็นไปได้ที่ AMD จะเพิ่มจำนวนคอร์ต่อ CCD เป็น 12 คอร์ และให้แคช L3 ขนาด 48 MB แก่ CCD ณ จุดนี้ เรายังไม่ทราบว่าคอร์ทั้ง 12 คอร์จะถูกจัดเรียงใน CCX เดียวที่มีแคช L3 ขนาด 48 MB แบบโมโนลิธิกหรือไม่ หรือจะมีเลย์เอาต์ CCX แบบคู่ โดยมี 6 คอร์ต่อ CCX ที่ใช้แคช L3 ขนาด 24 MB ต่อคอร์ การอัปเกรดครั้งใหญ่อีกอย่างหนึ่งของ "Medusa Ridge" คือไคลเอนท์ I/O die (cIOD) คาดว่า AMD จะสร้าง cIOD รุ่นใหม่บนโหนด EUV รุ่นใหม่ เช่น N5 ขนาด 5 นาโนเมตร หรือ N4P ขนาด 4 นาโนเมตร ซึ่งเป็นการอัปเกรดที่สำคัญจาก N6 ขนาด 6 นาโนเมตรในปัจจุบัน 1usmus กล่าวว่าเหตุผลสำคัญที่สุดที่ AMD อัปเดต cIOD คือสถาปัตยกรรมตัวควบคุมหน่วยความจำ คาดว่า AMD จะมอบสถาปัตยกรรมตัวควบคุมหน่วยความจำคู่ใหม่ให้กับ "Medusa Point" ยังคงมี DDR5 สองช่องต่อซ็อกเก็ต แต่ได้รับการออกแบบใหม่เพื่อเพิ่มความเร็วหน่วยความจำ ทำให้ AMD ไล่ตาม Intel ทันในด้านนี้ สำหรับเทคโนโลยีเพิ่มความถี่ CPU เช่น PBO และ Curve Optimizer คาดว่าจะไม่มีการอัปเดต และ 1usmus สรุปว่าการรองรับ Hydra น่าจะทำได้ง่ายกว่า

ที่มา : TechPowerUp

ที่มา : TechPowerUp