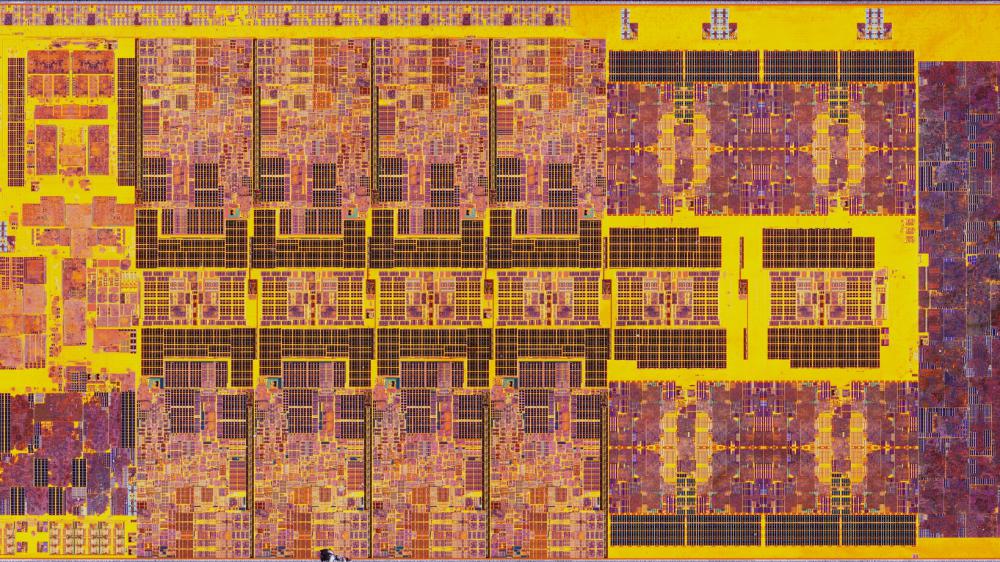

"Bartlett Lake-S" เป็นชิปที่น่าสนใจจาก Intel เนื่องจากโปรเซสเซอร์เดสก์ท็อป "Nova Lake-S" ที่มีแคช L3 ขนาดใหญ่จะยังไม่เปิดตัวก่อนกลาง/ปลายปี 2026 ชิปนี้สร้างขึ้นบนแนวคิดที่ว่า P-core "Raptor Cove" ให้ประสิทธิภาพการเล่นเกมเทียบเท่าหรือดีกว่า P-core "Lion Cove" ที่ติดตั้งใน "Arrow Lake-S" Intel คาดว่าสำหรับซิลิคอนโมโนลิธิกที่มีขนาดไดใกล้เคียงกับ "Raptor Lake-S" ซึ่งมี P-core 8 คอร์และคลัสเตอร์ E-core 4 คลัสเตอร์ Intel สามารถออกแบบซิลิคอนที่มี P-core 12 คอร์ที่มีจำนวน ring-stop เท่ากัน และใช้แคช L3 ขนาด 36 MB ร่วมกันได้ โพสต์ล่าสุดบน Twitter โดย Jaykihn เน้นย้ำถึงการก้าวขึ้นเป็น A0 ของซิลิคอนนี้ แต่ยังมีรายละเอียดเพิ่มเติมอีก นั่นคือ ดูเหมือนว่า Intel จะนำซิลิคอน "Raptor Lake" และ "Alder Lake" รุ่นเก่ากลับมาใช้ใหม่ในรุ่น "Bartlett Lake" และเรียกมันว่า "Bartlett Lake Hybrid"

โปรเซสเซอร์รุ่น "Bartlett Lake Hybrid" นี้จะนำชิป B0, C0 และ H0 กลับมาใช้ใหม่ ชิป B0 คือ "Raptor Lake-S" ดั้งเดิม ซึ่งมาพร้อมกับโครงสร้างแกนประมวลผล 8P+16E, แคช L3 ขนาด 36 MB, แคช L2 ขนาด 2 MB ต่อ P-core และแคช L2 ขนาด 4 MB ต่อคลัสเตอร์ E-core ส่วนซิลิคอน C0 พัฒนามาจาก "Alder Lake-S" โดยมีโครงสร้าง 8P+8E ที่มีแคช L2 ขนาด 1.25 MB ต่อ P-core และแคช L2 ขนาด 2 MB ต่อคลัสเตอร์ E-core พร้อมแคช L3 ขนาด 30 MB เดิมทีชิปซิลิกอน H0 ขับเคลื่อนครึ่งล่างของตระกูล Core เจนเนอเรชั่นที่ 12 โดยมี P-core จำนวน 6 คอร์ แต่ละคอร์มีแคช L2 ขนาด 1.25 MB ไม่มีคลัสเตอร์ E-core และมีแคช L3 ขนาด 18 MB

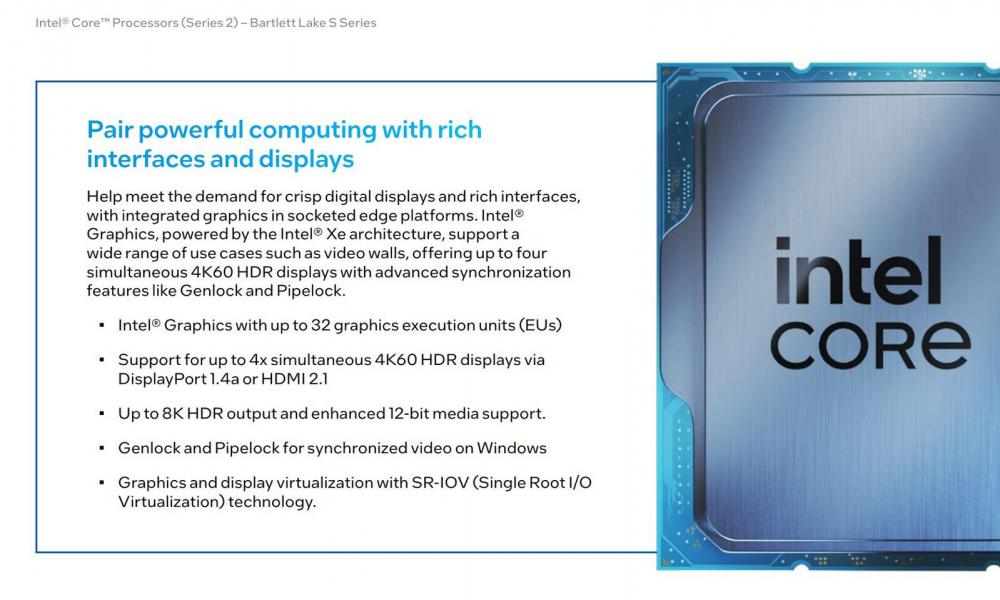

Intel จะไม่ทำตลาด "Bartlett Lake-S" ในฐานะซีรีส์ Core เจนเนอเรชั่นที่ 15 แต่จะเปลี่ยนไปใช้ชื่อใหม่ภายใต้ซีรีส์ Core 2 แต่ไม่มีส่วนขยายของแบรนด์ "Ultra" ซึ่งบ่งชี้ว่าไม่มี NPU แบบ on-die น่าเสียดายที่สื่อการตลาดที่รั่วไหลจาก Intel ชี้ให้เห็นว่าชิปนี้มุ่งเป้าไปที่ตลาด OEM และตลาดแบบฝังตัวเป็นหลัก ไม่ใช่ตลาดค้าปลีกแบบ DIY กล่าวอีกนัยหนึ่งคือ ยังไม่มีสัญญาณบ่งชี้ว่าชิปเดสก์ท็อปแบบค้าปลีกที่สามารถติดตั้งลงในอุปกรณ์ Socket LGA1700 ได้

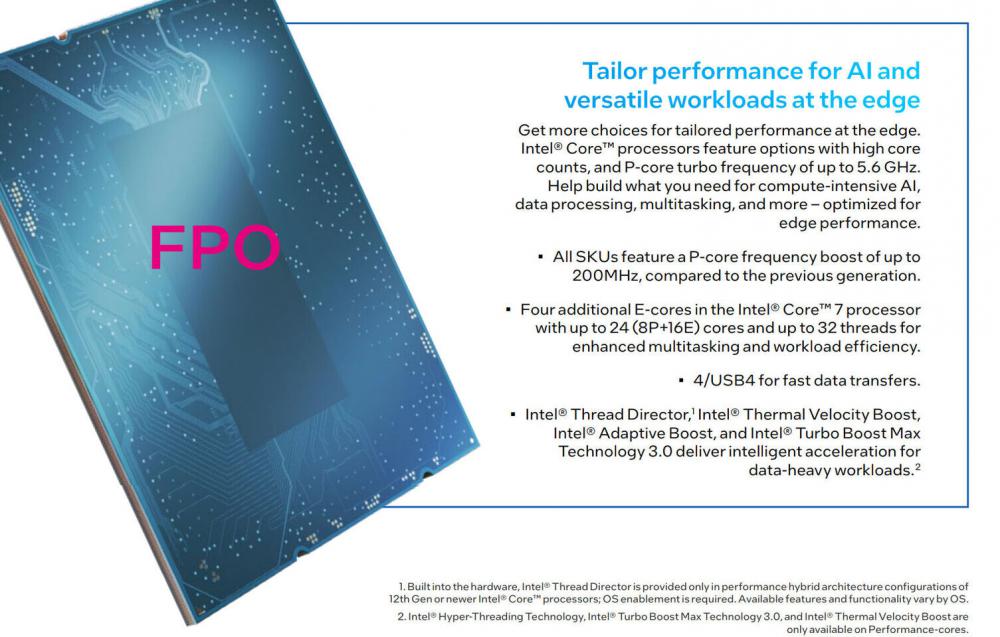

"Bartlett Lake-S" A0 จะเป็นโปรเซสเซอร์เดสก์ท็อปที่มีจำนวน P-core สูงสุดจาก Intel และจะเป็นโปรเซสเซอร์ที่มีจำนวน P-core สูงสุดภายในคอมพิวต์คอมเพล็กซ์เดียว (เช่น ใช้แคช L3 ร่วมกัน) ในทุกแบรนด์ เนื่องจากโปรเซสเซอร์เดสก์ท็อป AMD Ryzen แบบ 12 คอร์และ 16 คอร์ มีคอร์ที่แบ่งออกเป็นสองคอมพิวต์ในรูปแบบของ CCD สองตัว เธรดที่จะย้ายระหว่างคอร์ของ CCD ทั้งสองนั้นจำเป็นต้องเดินทางไปกลับที่ DRAM

ที่มา : TechPowerUp

ที่มา : TechPowerUp