ตามรายงานจากนักวิเคราะห์ชาวเกาหลี Kurnal บน X ระบุว่า Rapidus ผู้ผลิตชิปจากญี่ปุ่นที่กำลังก้าวเข้าสู่ตลาดการผลิตระดับนำ จะส่งมอบกระบวนการผลิต 2 นาโนเมตร (2nm) รุ่นใหม่ชื่อ 2HP ที่มีความหนาแน่นทรานซิสเตอร์ใกล้เคียงกับผู้นำตลาดอย่าง TSMC

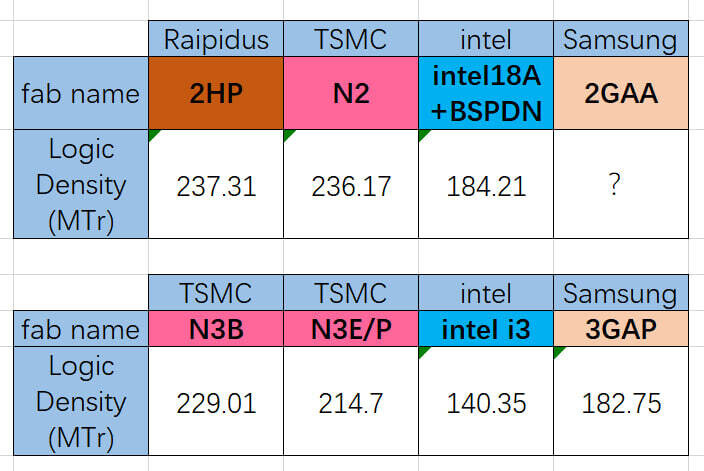

ข้อมูลเผยว่า Rapidus 2HP มีความหนาแน่นลอจิกอยู่ที่ 237.31 ล้านทรานซิสเตอร์ต่อมม² (MTr/mm²) ซึ่งแทบจะเทียบเท่ากับ TSMC N2 (236.17 MTr/mm²) และเหนือกว่า Intel 18A (ประมาณ 184.21 MTr/mm²) อย่างชัดเจน โดย Rapidus มุ่งเน้นไปที่ standard cells ความหนาแน่นสูง และ กระบวนการ front-end แบบ single-wafer ที่ช่วยให้นักวิศวกรสามารถปรับแต่งการผลิตได้ก่อนเข้าสู่การทำงานระดับใหญ่

ทั้งนี้ Rapidus ระบุว่าชิปทดสอบ 2nm gate-all-around ที่ผลิตด้วยเครื่อง ASML EUV สามารถผ่านเกณฑ์ทางไฟฟ้าแล้ว โดยบริษัทมีแผนจะปล่อย Process Design Kit (PDK) ในช่วงต้นปี 2026 และตั้งเป้าเริ่มการผลิตระดับปริมาณสูง (High-Volume Production) ที่โรงงาน IIM-1 ภายในปี 2027 โดยกำลังผลิตคาดว่าจะอยู่ที่ราว 25,000 แผ่นเวเฟอร์ต่อเดือน

นอกเหนือจากความหนาแน่น Rapidus ยังเน้นความเร็วและความยืดหยุ่น โดยแม้จะยังช้ากว่า TSMC ราว 1–2 เจนเนอเรชันในปี 2027 แต่บริษัทสัญญาว่าจะลด ระยะเวลาการผลิต (cycle time) จากราว 120 วันเหลือเพียง 50 วัน และสามารถเร่งงานด่วน ("hot lot") ได้ใน 15 วัน เท่านั้น

เพื่อให้ทำได้จริง Rapidus กำลังสร้าง ecosystem แบบ custom ร่วมกับ OSATs, ผู้พัฒนา EDA, ซัพพลายเออร์ IP และผู้ผลิตวัสดุ พร้อมได้รับการสนับสนุนจากรัฐบาลญี่ปุ่นและความสนใจจากบริษัทคอมพิวต์รายใหญ่ อย่างไรก็ตาม ความหนาแน่นเพียงอย่างเดียวไม่พอ ปัจจัยสำคัญจะอยู่ที่ ประสิทธิภาพต่อวัตต์ ความเสถียรของซัพพลายเชน และอัตราผลผลิตที่ทำซ้ำได้ ว่า Rapidus จะสามารถเปลี่ยนจากชิปต้นแบบไปสู่การผลิตระดับอุตสาหกรรมได้หรือไม่

ที่มา : TechPowerUp