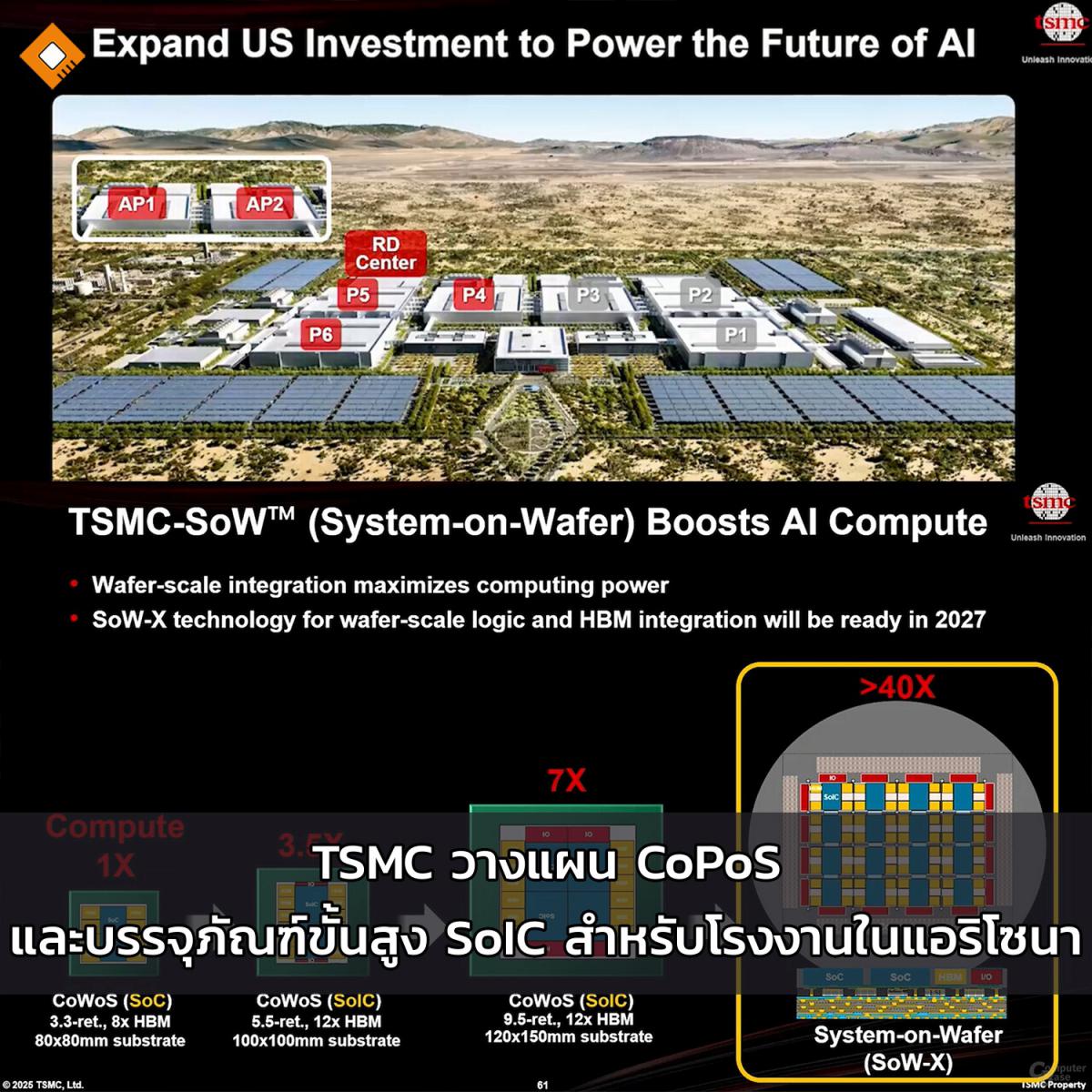

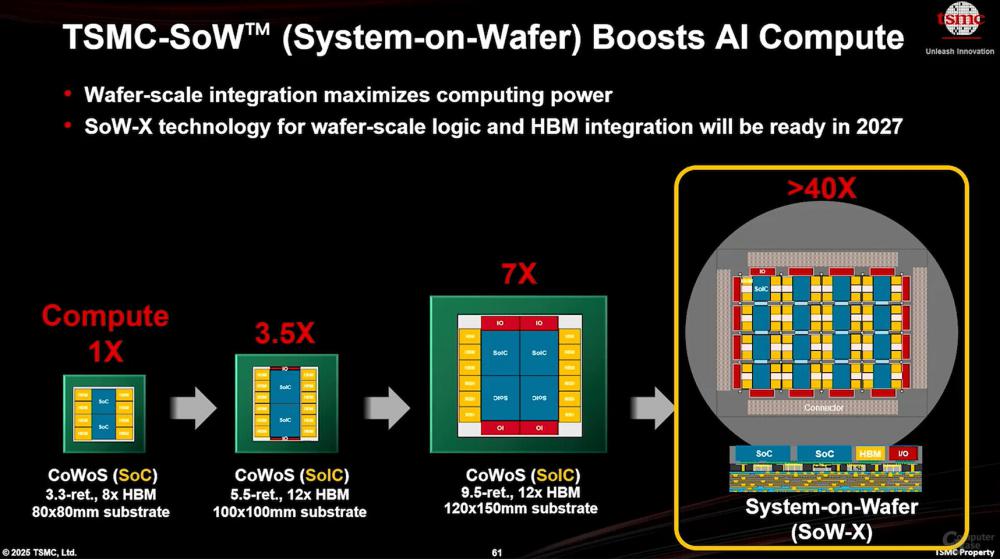

TSMC วางแผนที่จะขยายโรงงานในรัฐแอริโซนาด้วยบรรจุภัณฑ์ขั้นสูง โดยการสร้างอาคารเฉพาะสองหลังใกล้กับโรงงาน Fab 21 โรงงานแห่งแรกคือ Advanced Packaging Facility 1 (AP1) มีกำหนดเริ่มก่อสร้างในปี 2571 พร้อมกับโรงงาน Fab 21 เฟส 3 ซึ่งจะผลิตชิปบนโหนด N2 (2 นาโนเมตร) และอาจรวมถึงกระบวนการ A16 ด้วย ส่วนโครงสร้างที่สองคือ AP2 จะตามมาพร้อมกับการขยายโรงงานในภายหลัง (เฟส 4 และ 5) แม้ว่าจะยังไม่มีการยืนยันวันที่แน่นอน โรงงานทั้งสองแห่งจะมุ่งเน้นไปที่ System-on-Integrated-Chips (SoIC) และเทคโนโลยี Chip-on-Panel-on-Substrate (CoPoS) ที่กำลังเกิดขึ้น SoIC ใช้ vias ซิลิคอนแบบ through-silicon เพื่อซ้อนแคชหรือหน่วยความจำใต้แกนประมวลผลโดยตรง ซึ่งเป็นเทคนิคที่ได้รับการพิสูจน์แล้วในโปรเซสเซอร์ Ryzen X3D ของ AMD ในทางตรงกันข้าม CoPoS จะมาแทนที่เวเฟอร์ทรงกลมแบบเดิมด้วยแผงสี่เหลี่ยมขนาดประมาณ 310x310 มม. การเปลี่ยนแปลงนี้ทำให้พื้นที่ซับสเตรตที่ใช้งานได้เพิ่มขึ้นมากกว่าห้าเท่า ทำให้สามารถผสานรวมหน่วยความจำแบนด์วิดท์สูง ชิปเล็ต I/O และไทล์ประมวลผลหลายตัวได้อย่างหนาแน่นยิ่งขึ้น พร้อมกับลดต้นทุนต่อหน่วย เบื้องหลัง TSMC จะเริ่มสายการผลิตนำร่อง CoPoS เร็วที่สุดในปี 2569 โดยมีเป้าหมายที่จะเสร็จสิ้นการตรวจสอบความถูกต้องของพันธมิตรภายในปลายปี 2570 การผลิตนำร่องนี้ออกแบบมาเพื่อรับมือกับความท้าทายด้านการผลิตและคว้าชัยชนะด้านการออกแบบกับลูกค้ารายใหญ่ ได้แก่ NVIDIA, AMD และ Apple เพื่อให้มั่นใจว่าบรรจุภัณฑ์ที่ประกอบในสหรัฐอเมริกาจะมีมาตรฐานด้านประสิทธิภาพและความน่าเชื่อถือเช่นเดียวกับในไต้หวัน คาดว่าการผลิตจำนวนมากที่ AP1 จะเริ่มเพิ่มขึ้นในช่วงปลายปี 2572 หรือต้นปี 2573 ซึ่งสอดคล้องกับแนวทางปฏิบัติด้านระยะเวลาการผลิตสองปีของ TSMC นั่นคือ นวัตกรรมโหนดและบรรจุภัณฑ์ใหม่จะเปิดตัวบนเกาะไต้หวันก่อนที่จะนำไปขยายไปยังต่างประเทศ

ที่มา : TechPowerUp

ที่มา : TechPowerUp