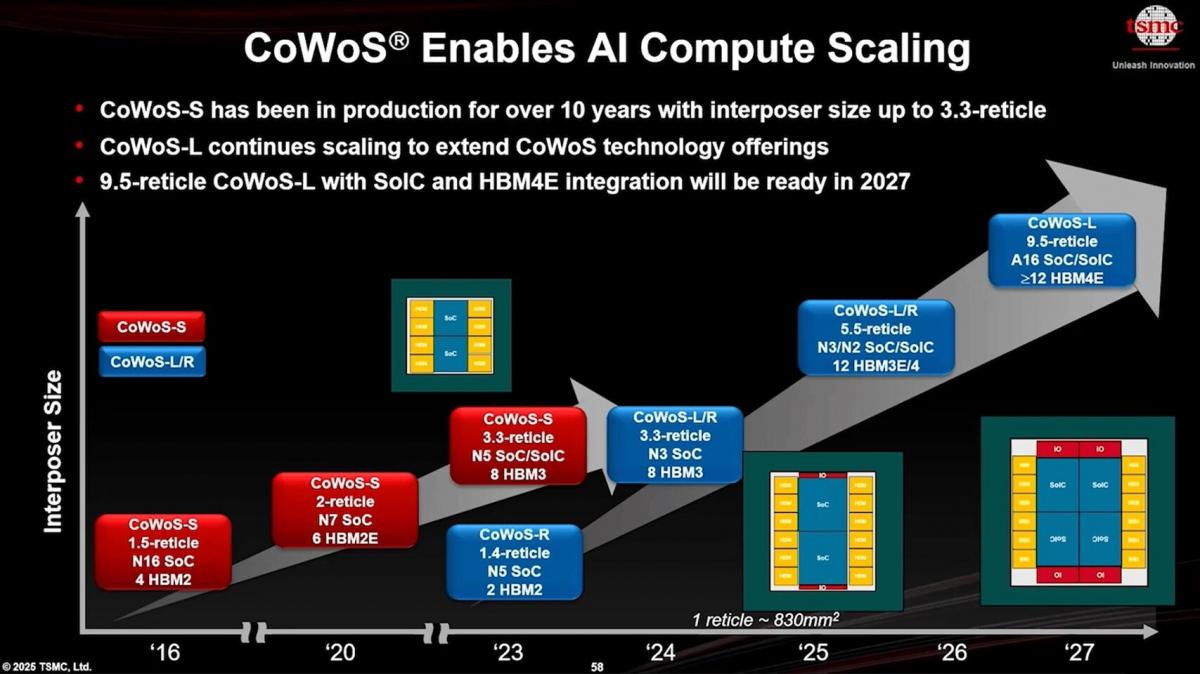

ในงานสัมมนาเทคโนโลยีประจำปีนี้ TSMC เปิดเผยแผนงานหลายปีที่น่าสนใจสำหรับเทคโนโลยีบรรจุภัณฑ์ของตน กลยุทธ์ของ TSMC แบ่งออกเป็นสองประเภทหลัก ได้แก่ บรรจุภัณฑ์ขั้นสูงและระบบบนเวเฟอร์ ย้อนกลับไปในปี 2016 CoWoS-S เปิดตัวด้วยสแต็ก HBM สี่ชุดที่จับคู่กับไดย์คอมพิวเตอร์ N16 บนอินเตอร์โพเซอร์ที่จำกัดเรติเคิล 1.5 เท่า ซึ่งถือเป็นความสำเร็จที่น่าประทับใจในเวลานั้น เร็ว ๆ นี้ในปี 2025 และปัจจุบัน CoWoS-S รองรับชิป HBM แปดชิปร่วมกับไทล์คอมพิวเตอร์ N5 และ N4 ภายในงบประมาณเรติเคิล 3.3 เท่า CoWoS-R ซึ่งเป็นรุ่นต่อจากนี้จะเพิ่มแบนด์วิดท์ของการเชื่อมต่อและทำให้เข้ากันได้กับโหนด N3 โดยไม่เปลี่ยนข้อจำกัดเรติเคิลนั้น เมื่อมองไปถึงปี 2027 TSMC จะเปิดตัว CoWoS-L ชิปเล็ต N3-node ขนาดใหญ่เป็นอันดับแรก ตามด้วยไทล์ N2-node ไดย์ I/O หลายตัว และสแต็ก HBM3E หรือ HBM4 มากถึง 12 ชุด ซึ่งทั้งหมดอยู่ภายในเพดานเรติเคิล 5.5 เท่า แทบไม่น่าเชื่อว่าสแต็ก HBM แปดชุดเคยฟังดูทะเยอทะยาน แต่ตอนนี้กลายเป็นเพียงจุดเริ่มต้นสำหรับเครื่องเร่งความเร็ว AI รุ่นถัดไปที่ได้รับแรงบันดาลใจจาก Instinct MI450X ของ AMD และ Vera Rubin ของ NVIDIA Fan-Out หรือ InFO แบบบูรณาการเพิ่มมิติใหม่ด้วยชุดประกอบ 3D ที่ยืดหยุ่นได้ บริดจ์ InFO ดั้งเดิมนั้นขับเคลื่อนการ์ด Instinct ของ AMD อยู่แล้ว ปลายปีนี้ InFO-POP (แพ็คเกจต่อแพ็คเกจ) และ InFO-2.5D มาถึง ซึ่งสัญญาว่าจะมีการวางชิปที่หนาแน่นยิ่งขึ้นและปลดล็อกศักยภาพการปรับขนาดใหม่บนแพ็คเกจเดียว โดยไม่ต้องพึ่งแพ็คเกจ 2D และ 2.5D ที่เราเคยใช้ โดยจะเข้าสู่มิติที่สาม ในระดับเวเฟอร์ กลุ่มผลิตภัณฑ์ System-on-Wafer ของ TSMC อย่าง SoW-P และ SoW-X ได้เติบโตจากเอ็นจิ้น AI เฉพาะทางไปสู่แผนงานที่ครอบคลุมซึ่งสะท้อนถึงความก้าวหน้าของโหนดตรรกะ ปีนี้ถือเป็นการเปิดตัวสแต็ก SoIC ชุดแรกจาก N3 ถึง N4 โดยแต่ละไทล์มีขนาดสูงสุด 830 มม.² และไม่มีข้อจำกัดที่ชัดเจนเกี่ยวกับขนาดส่วนบนของไดย์ ซึ่งแนวโน้มดังกล่าวชี้ให้เห็นถึงแพ็คเกจขนาดใหญ่และหนาแน่นเป็นพิเศษ ซึ่งเป็นสิ่งที่ศูนย์ข้อมูล HPC และ AI จะต้องการในอีกไม่กี่ปีข้างหน้า

ที่มา : TechPowerUp