AMD ในเซสชันถามตอบเชิงลึกด้านสถาปัตยกรรมกับสื่อมวลชน ยืนยันว่าคอร์ "Zen 5" และ "Zen 5c" บนซิลิคอน "Strix Point" มีเฉพาะเส้นทางข้อมูล FPU แบบกว้าง 256 บิตเท่านั้น ซึ่งแตกต่างจาก "Zen 5" แกนประมวลผลในโปรเซสเซอร์เดสก์ท็อป "Granite Ridge" Ryzen 9000 “Zen 5c ที่ใช้ใน Strix มีเส้นทางข้อมูล 256 บิต และ Zen 5 ที่ใช้ใน Strix ก็เช่นกัน” Mike Clark เพื่อนร่วมงานองค์กรของ AMD และหัวหน้าสถาปัตยกรรมของแกน CPU "Zen" กล่าว “ดังนั้นจึงไม่มีเดลต้าเมื่อคุณเลื่อนไปมา [การโยกย้ายเธรดระหว่างคอมเพล็กซ์ Zen 5 และ Zen 5c] ในปริมาณการประมวลผลแบบเวกเตอร์” เขากล่าวเสริม

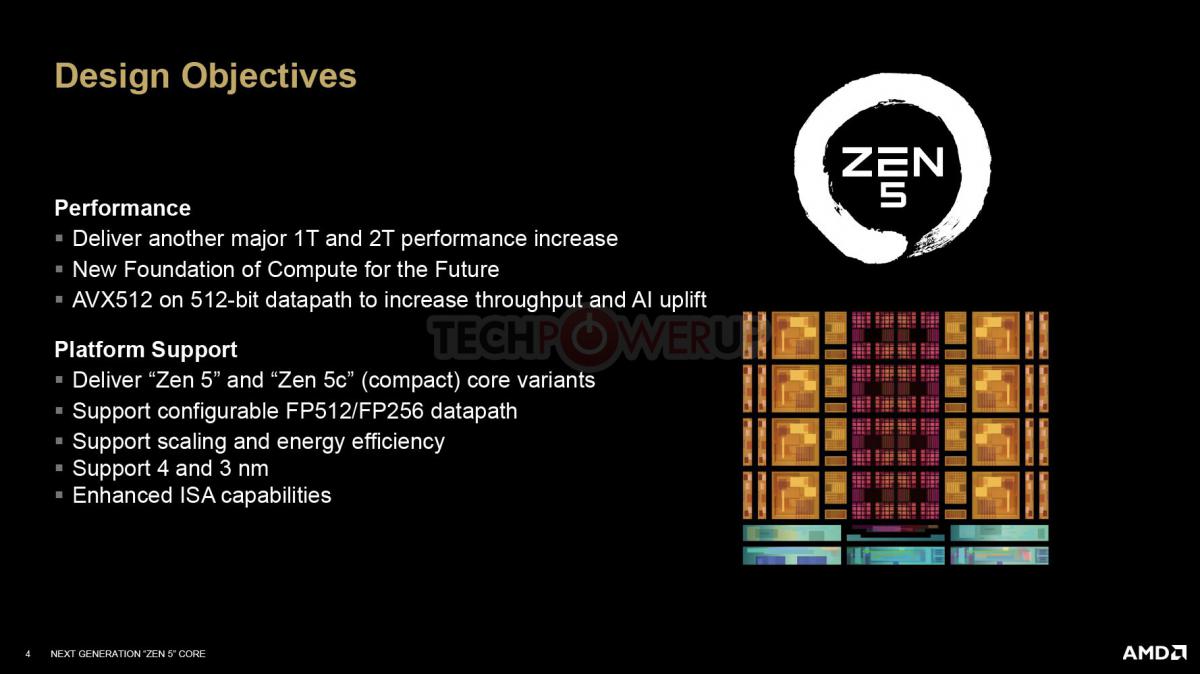

ดูเหมือนว่า AMD จะไม่ได้ปิดการใช้งานฟีเจอร์ที่มีอยู่จริง แต่ทางบริษัทได้พัฒนาคอร์ "Zen 5" และ "Zen 5c" ที่แตกต่างกันออกไป ซึ่งทางกายภาพนั้นขาดเส้นทางข้อมูล 512 บิต “และคุณจะได้รับความได้เปรียบในพื้นที่เพื่อให้สามารถขยายขนาดได้อีกสักหน่อย” คลาร์กกล่าวต่อ นี่แสดงให้เห็นว่าแกน "Zen 5" และ "Zen 5c" บน "Strix Point" นั้นมีขนาดเล็กกว่าแกนบน CCD 8 คอร์ "Eldora" 4 นาโนเมตรที่มีอยู่ใน "Granite Ridge" และรุ่นหลักบางรุ่น ของโปรเซสเซอร์เซิร์ฟเวอร์ EPYC "Turin" รุ่นที่ 5 ที่กำลังจะมาถึง

สิ่งที่น่าสนใจประการหนึ่งของสถาปัตยกรรมไมโคร "Zen 5" คือหน่วยจุดลอยตัว ซึ่งรองรับ AVX512 ด้วยเส้นทางข้อมูล 512 บิตเต็มรูปแบบ ในการเปรียบเทียบ "Zen 4" รุ่นก่อนหน้าจัดการ AVX512 โดยใช้ FPU 256 บิตแบบ dual-pumped FPU 512 บิตใหม่ ขึ้นอยู่กับปริมาณงานที่แน่นอนและปัจจัยอื่นๆ เร็วกว่า "Zen 4" ประมาณ 20-40% ที่ปริมาณงานจุดลอยตัว 512 บิต ซึ่งเป็นเหตุผลว่าทำไม "Zen 5" จึงคาดว่าจะได้รับผลกำไรอย่างมีนัยสำคัญ ในประสิทธิภาพการอนุมานของ AI ตลอดจนการผ่านเกณฑ์มาตรฐานที่ใช้ AVX512

เราไม่แน่ใจว่าการขาดเส้นทางข้อมูล FP 512 บิตส่งผลต่อประสิทธิภาพของคำสั่งที่เกี่ยวข้องกับการเร่งความเร็ว AI อย่างไร เนื่องจาก "Strix Point" ได้รับการออกแบบเป็นหลักสำหรับพีซี AI ที่พร้อมใช้งาน Microsoft Copilot+ เป็นไปได้ว่า AVX512 และ AVX-VNNI กำลังทำงานบนพาธข้อมูล 256 บิตแบบ dual-pumped คล้ายกับที่ทำบน "Zen 4" การทำเช่นนี้อาจมีข้อดีด้านประสิทธิภาพ/วัตต์ ซึ่งอาจเกี่ยวข้องกับแพลตฟอร์มพกพา

ที่มา : TechPowerUp

ที่มา : TechPowerUp