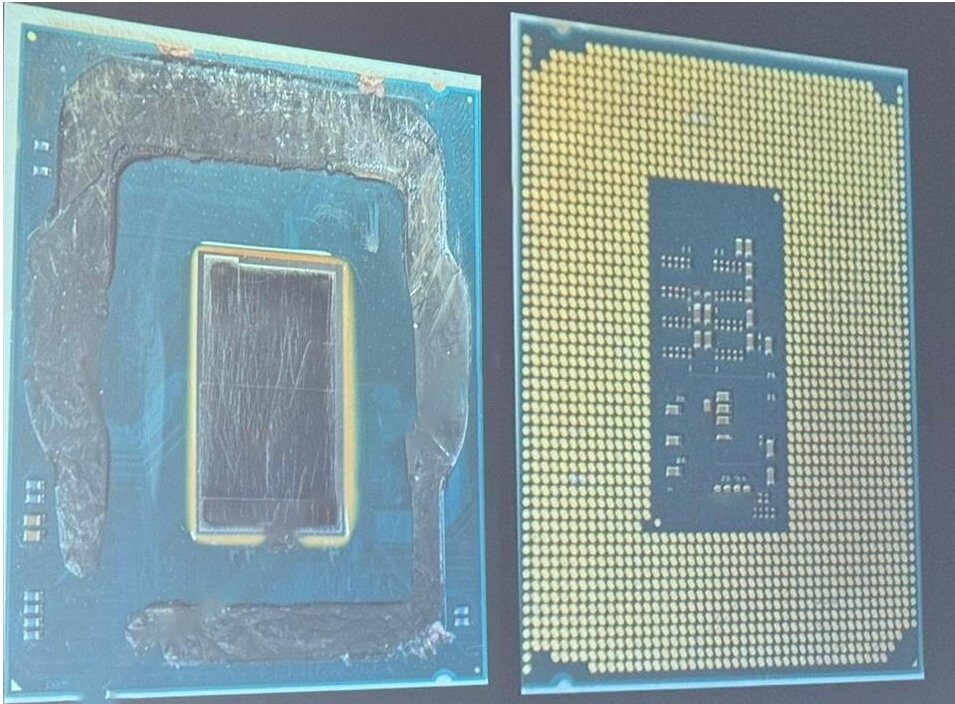

ภาพแรกๆ ของโปรเซสเซอร์ Intel Core Ultra 9 285K "Arrow Lake-S" ที่ถอดฝาออกบางส่วนปรากฏบนเว็บไซต์ ซึ่งยืนยันการออกแบบโปรเซสเซอร์ที่ใช้ชิปเล็ตแบบแยกส่วน Intel ได้เปลี่ยนมาใช้โปรเซสเซอร์ที่ใช้ชิปเล็ตด้วย Core Ultra "Meteor Lake" ซึ่งทำให้สามารถสร้างบล็อก IP เฉพาะของโปรเซสเซอร์บนโหนดหล่อต่างๆ ได้ ทำให้มั่นใจได้ว่าโหนดที่ไม่ต้องการโหนดขั้นสูงที่สุดสามารถใช้โหนดที่เก่ากว่าเล็กน้อยได้ จึงทำให้ Intel สามารถเพิ่มประสิทธิภาพของโหนดขั้นสูงนั้นได้สูงสุด ภาพของไดย์เผยให้เห็นระดับการแยกส่วนที่คล้ายคลึงกับ "Meteor Lake" มากกว่าโปรเซสเซอร์มือถือ Core Ultra 200V "Lunar Lake" รุ่นล่าสุด

ด้วย "Lunar Lake" Intel ได้รวมสิ่งต่างๆ สองสามอย่างเข้าด้วยกันใหม่ "Lunar Lake" มีเพียงสองไทล์เท่านั้น คือ ไทล์ SoC และไทล์ I/O ไทล์ SoC ขนาด 3 นาโนเมตรประกอบด้วยคอมเพลกซ์ CPU, iGPU ขนาดใหญ่ และ NPU ระดับ 40 TOPS ขนาดใหญ่ ซึ่งทั้งหมดใช้พื้นที่ไดย์ร่วมกันกับตัวควบคุมหน่วยความจำ และคอมเพลกซ์รูท PCIe ไทล์ I/O ขนาด 6 นาโนเมตรที่เล็กกว่าประกอบด้วย PHY ของอินเทอร์เฟซ I/O ต่างๆ ชิป "Arrow Lake" ดูเหมือนจะมีระดับการแยกส่วนที่คล้ายกันกับ "Meteor Lake" เราสามารถเห็นไทล์อย่างน้อยห้าไทล์วางอยู่บนไทล์พื้นฐานของ Foveros รูปภาพไม่มีคำอธิบายประกอบสำหรับไทล์ต่างๆ แต่รายงานล่าสุดของ Moore's Law is Dead และ Jay Kihn ได้ให้ความกระจ่างว่าไทล์เหล่านี้คืออะไร

รายงาน MLID ระบุว่าจะมีไทล์ Compute ซึ่งประกอบด้วยคอร์ CPU ไทล์ SoC ไทล์ Graphics ไทล์ I/O แบบแยกส่วน และไทล์จำลองบางส่วนที่ให้การเสริมความแข็งแรงเชิงโครงสร้าง ทำให้ชิปมีรูปร่างเป็นสี่เหลี่ยมผืนผ้า การรั่วไหลของ Jay Kihn ชี้ไปที่กระเบื้อง Compute ที่มี P-core และคลัสเตอร์ E-core ที่จัดเรียงใน ring-bus ทั่วไป โดยแบ่งปันแคช L3 คล้ายกับสิ่งต่างๆ ในกระเบื้อง Compute ของ "Meteor Lake" กระเบื้องนี้ประกอบด้วย P-core "Lion Cove" จำนวน 8 คอร์ โดยแต่ละคอร์มีแคช L2 เฉพาะขนาด 3 MB (เราทราบเรื่องนี้จากการเจาะลึกทางเทคนิคของ Lunar Lake) และคลัสเตอร์ E-core "Skymont" จำนวน 4 คลัสเตอร์ โดยแต่ละคลัสเตอร์มีแคช L2 ที่ใช้ร่วมกันขนาด 4 MB คอร์ CPU ทั้งหมดใช้แคช L3 ขนาด 36 MB ร่วมกัน

กระเบื้อง Compute เชื่อมต่อกับกระเบื้อง SoC ซึ่งประกอบด้วยตัวควบคุมหน่วยความจำ DDR5, รูทคอมเพล็กซ์ PCIe Gen 5, โปรเซสเซอร์ความปลอดภัย, ตัวควบคุมการแสดงผล และเอ็นจิ้นเร่งความเร็วสื่อ นอกจากนี้ยังมี "คอมเพล็กซ์ AI" ซึ่งอาจเป็น NPU ได้เป็นอย่างดี ยังต้องรอดูว่านี่คือ NPU 4 ขนาดใหญ่กว่าที่นำมาจาก "Lunar Lake" ซึ่งตรงตามข้อกำหนดของ Microsoft Copilot+ หรือไม่ ไทล์ SoC จะแสดง I/O บางส่วนออกมา เช่น หน่วยความจำ DDR5 และส่วนหนึ่งของ PCIe แต่จะต้องอาศัยไทล์ I/O แบบแยกส่วนเพื่อให้มีการเชื่อมต่อ PCIe มากขึ้น และ Thunderbolt ในตัว

สุดท้ายคือไทล์กราฟิก ซึ่งประกอบด้วย iGPU โดยหลักแล้วคือคอร์ Xe และฮาร์ดแวร์ทั้งหมดที่ iGPU ต้องการในกระบวนการเรนเดอร์กราฟิก รวมถึงแคช L3 ของตัวเอง ตัวควบคุมการแสดงผลและตัวเร่งความเร็วสื่อจะอยู่ในไทล์ SoC และ I/O การแสดงผลจะอยู่ในไทล์ I/O แบบแยกส่วน เมื่อพิจารณาขนาดของไทล์กราฟิกแล้ว หากเราเดาดู เวอร์ชันเดสก์ท็อปของ "Arrow Lake" น่าจะไม่มี iGPU ขนาดใหญ่มากนัก อาจมีคอร์ Xe เพียงสองคอร์ ในทางตรงกันข้าม "Lunar Lake" มี iGPU ขนาดใหญ่ที่มีคอร์ Xe 8 คอร์ เนื่องจากแนวคิดเบื้องหลัง "Lunar Lake" คือโน้ตบุ๊กแบบบางและเบาที่ไม่มีกราฟิกแยก

ที่มา : TechPowerUp

ที่มา : TechPowerUp