ขณะที่โปรเซสเซอร์เดสก์ท็อป Core Ultra "Arrow Lake-S" ของ Intel ใกล้จะเปิดตัว ASUS China ก็ได้เผยแพร่วิดีโอแนะนำเกี่ยวกับมาเธอร์บอร์ดชิปเซ็ต Z890 ที่พร้อมสำหรับโปรเซสเซอร์เหล่านี้ ซึ่งรวมถึงข้อมูลทางเทคนิคของโปรเซสเซอร์เดสก์ท็อปแบบไทล์ตัวแรกของ Intel ซึ่งรวมถึงภาพไดย์แบบละเอียดของไทล์ต่างๆ นี่เป็นสิ่งที่ต้องไม่เพียงแต่เปิดฝาโปรเซสเซอร์ออก (ถอดตัวกระจายความร้อนในตัวออก) เท่านั้น แต่ยังต้องทำความสะอาดชั้นบนสุดของไดย์เพื่อเปิดเผยส่วนประกอบต่างๆ ที่อยู่ด้านล่างด้วย

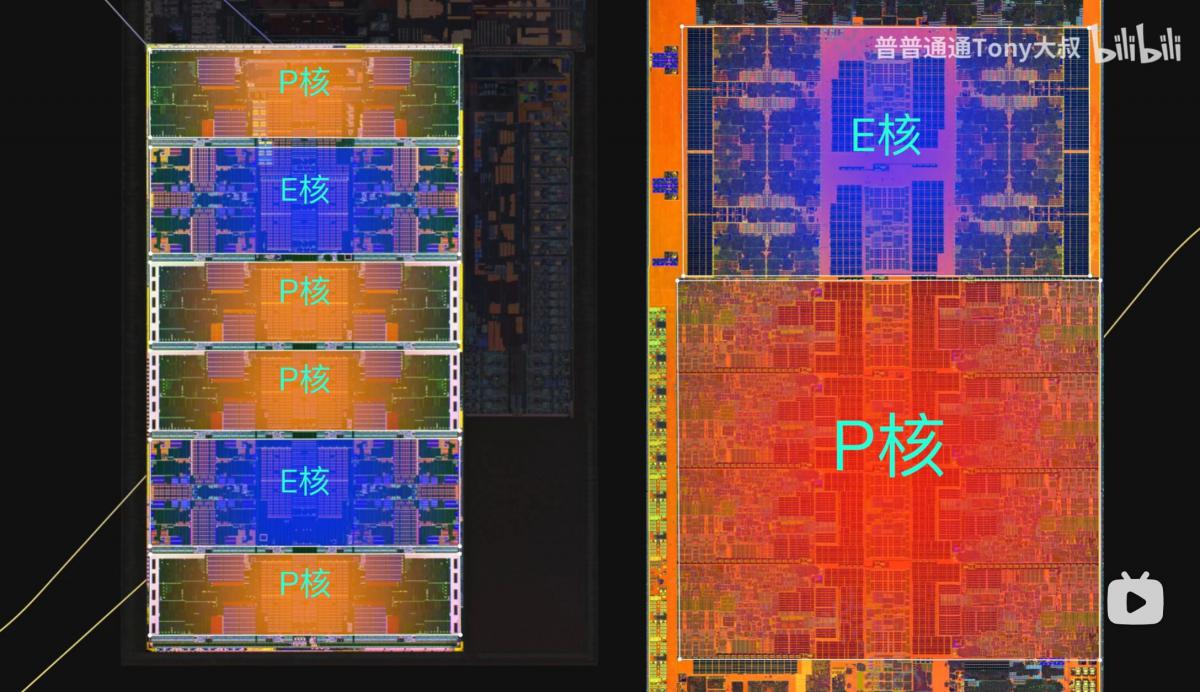

ภาพไดย์ของชิปทั้งหมดทำให้เราเห็นไทล์ลอจิกหลักทั้งสี่ไทล์ ได้แก่ Compute, Graphics, SoC และ I/O ซึ่งวางอยู่บนไทล์พื้นฐานของ Foveros บทความของเราเมื่อต้นสัปดาห์นี้จะพูดถึงพื้นที่ไดย์ของไทล์แต่ละไทล์และไทล์พื้นฐาน ไทล์ Compute สร้างขึ้นบนโหนดหล่อที่ทันสมัยที่สุดในบรรดาไทล์ทั้งสี่ไทล์ นั่นคือ TSMC N3B ขนาด 3 นาโนเมตร ต่างจาก "Raptor Lake-S" และ "Alder Lake-S" รุ่นเก่ากว่า คลัสเตอร์ P-core และ E-core จะไม่รวมตัวกันที่ปลายทั้งสองข้างของคอมเพล็กซ์ CPU ใน "Arrow Lake-S" พวกมันจะเรียงกันแบบสลับกัน โดยมี P-core เรียงเป็นแถว ตามด้วยคลัสเตอร์ E-core เรียงเป็นแถว ตามด้วย P-core สองแถว จากนั้นจึงเป็นคลัสเตอร์ E-core อีกแถวหนึ่ง ก่อนถึงแถวสุดท้ายของ P-core เพื่อให้ได้จำนวนคอร์ทั้งหมด 8P+16E การจัดเรียงนี้จะช่วยลดความเข้มข้นของความร้อนเมื่อ P-core ถูกโหลด (เช่น เมื่อเล่นเกม) และช่วยให้แต่ละคลัสเตอร์ E-core อยู่ห่างจาก P-core เพียงสต็อปริงบัสเดียว ซึ่งควรจะปรับปรุงเวลาแฝงของการไมเกรชันเธรดได้ ส่วนกลางของไทล์มีริงบัสนี้และแคช L3 ขนาด 36 MB ที่แชร์กันระหว่าง P-core และคลัสเตอร์ E-core

ถัดไปคือไทล์ SoC ชิปเล็ตนี้สร้างขึ้นบนโหนด DUV TSMC N6 ขนาด 6 นาโนเมตร ขอบทั้งสองด้านของไทล์มี PHY สำหรับอินเทอร์เฟซ I/O ต่างๆ ด้านหนึ่งมี DDR5 PHY แบบดูอัลแชนเนล ในขณะที่อีกด้านหนึ่งมีส่วนหนึ่งของ PCI-Express PHY ของชิป ไทล์ SoC จะแสดงเลน PCIe Gen 5 จำนวน 16 เลนสำหรับอินเทอร์เฟซ PEG (สล็อต x16 บนเมนบอร์ดของคุณ) ไทล์ I/O จะแสดงเลน PCIe Gen 5 จำนวน 4 เลน และเลน PCIe Gen 4 จำนวน 4 เลน นอกเหนือจากบัสชิปเซ็ต DMI 4.0 x8 ไทล์ Gen 4 x4 จาก I/O สามารถกำหนดค่าใหม่เป็น Thunderbolt 4 หรือ USB4 ได้ ไทล์ SoC ยังประกอบด้วยหน่วย NPU 3 ซึ่งดูเหมือนว่าจะนำมาจากไทล์ SoC ของ "Meteor Lake" โดยมีทรูพุตสูงสุดที่ 13 AI TOPS นอกจากนี้ ไทล์ SoC ยังประกอบด้วยโปรเซสเซอร์รักษาความปลอดภัยของแพลตฟอร์มชิป และส่วนประกอบที่เกี่ยวข้องบางส่วนของ iGPU ได้แก่ เอ็นจิ้นการแสดงผล ตัวเร่งความเร็วสื่อ และ I/O การแสดงผล

สุดท้ายคือไทล์กราฟิก Intel สร้างไทล์นี้บนกระบวนการ TSMC N5 5 นาโนเมตรขั้นสูง (กระบวนการเดียวกับที่ใช้สร้าง GPU NVIDIA Ada และ AMD RDNA 3 ในปัจจุบัน) ไทล์ที่เพรียวบางนี้มีเพียงคอร์ Xe 4 คอร์ที่มีให้สำหรับ iGPU รุ่นนี้ และเครื่องเรนเดอร์กราฟิก