มีรายงานว่า TSMC กำลังรับมือกับปริมาณออเดอร์จำนวนมากจากลูกค้ามากกว่า 15 ราย ที่กำลังออกแบบชิปบนเทคโนโลยีการผลิตล่าสุด “N2” หรือ 2 นาโนเมตร

จากข้อมูลของ Ahmad Khan และ Bren Higgins แห่ง KLA ระบุว่า เทคโนโลยี N2 ได้รับความสนใจอย่างมาก โดยในจำนวนนี้มีถึง 10 รายที่เน้นไปที่งานออกแบบสำหรับ High-Performance Computing (HPC) ซึ่งมีความต้องการประสิทธิภาพสูงเป็นพิเศษ ลูกค้ารายใหญ่ที่คาดว่าจะเข้ามาใช้บริการมีทั้ง Intel, NVIDIA, AMD รวมถึงสตาร์ทอัพด้านเซมิคอนดักเตอร์ ขณะที่อีกส่วนหนึ่งน่าจะเป็นกลุ่มที่เน้นดีไซน์สำหรับอุปกรณ์พกพา เช่น Apple, Qualcomm และ MediaTek

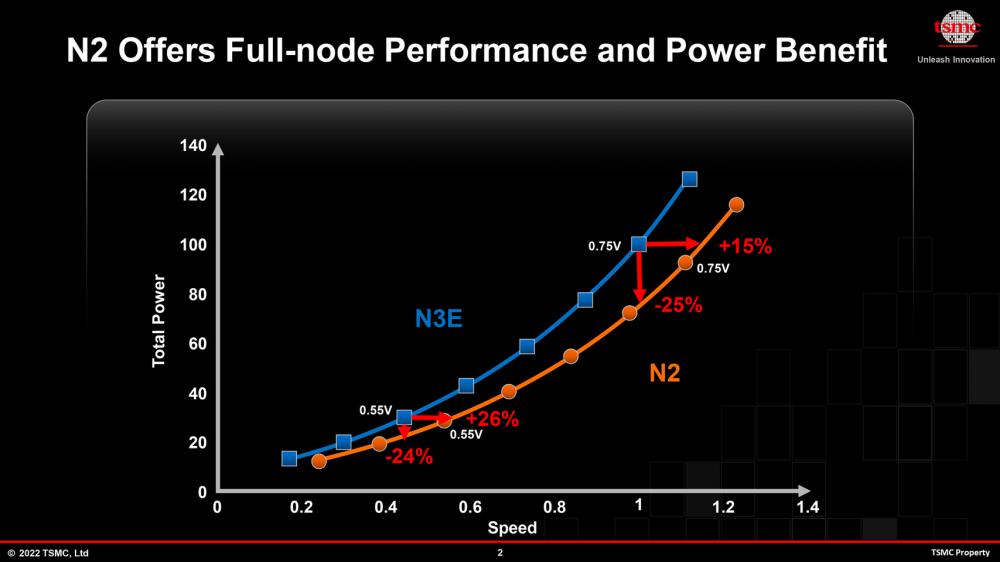

จุดเด่นของ N2 node

-

ประสิทธิภาพด้านพลังงานสูง

-

ความหนาแน่นทรานซิสเตอร์ 236.17 ล้านตัวต่อ 1 มม²

-

เหมาะสำหรับทั้งงาน HPC/AI และชิปมือถือ

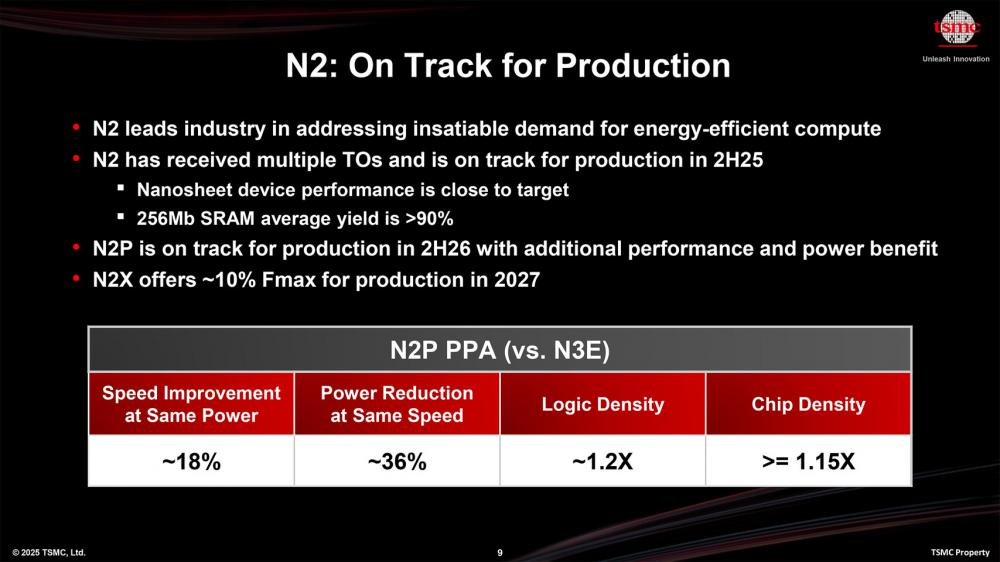

เดิมที TSMC วางแผนจะนำเทคโนโลยี backside power delivery network มาใช้กับ N2 แต่สุดท้ายได้เลื่อนไปใช้กับ A16 node แทน ส่วน N2 จะใช้โครงสร้าง GAA (Gate All Around) FET เพื่อควบคุมการรั่วของประตูทรานซิสเตอร์ได้ดีกว่า และเป็นการก้าวข้ามข้อจำกัดของ FinFET ที่ถึงขีดสุดแล้วในการย่อขนาด

TSMC วางกำหนดการเปิดตัวเชิงพาณิชย์ของ N2 node ในช่วงครึ่งหลังของปี 2026 และคาดว่าบริษัทเทคโนโลยีรายใหญ่จะเริ่มนำมาใช้งานจริงในช่วงต้นปี 2027

ที่มา : TechPowerUp