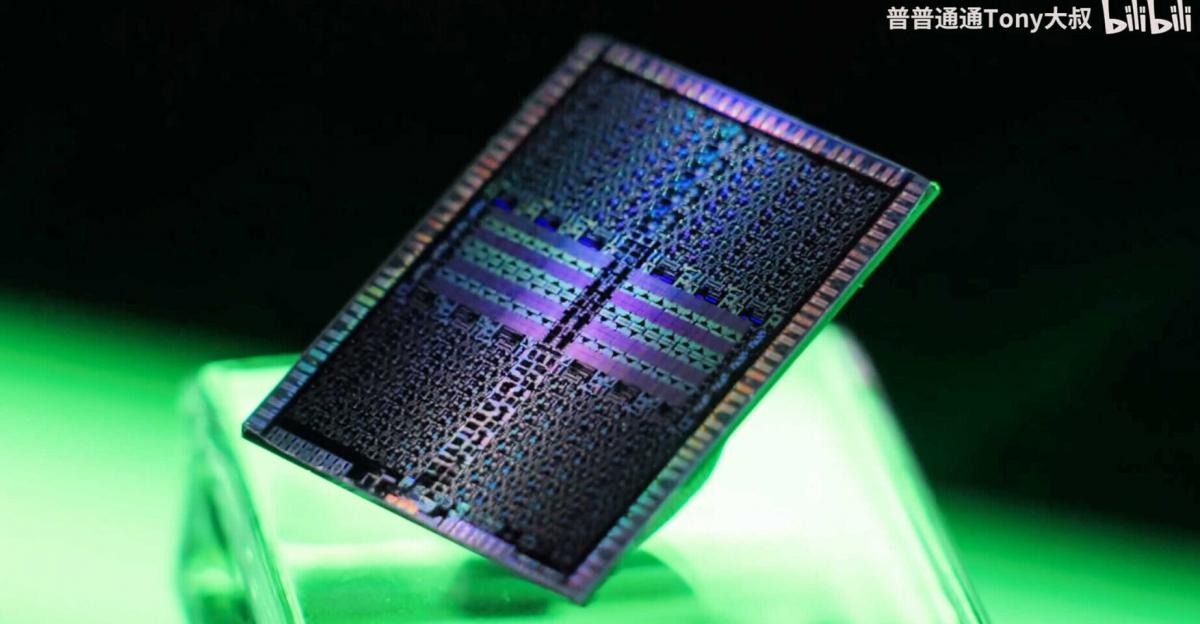

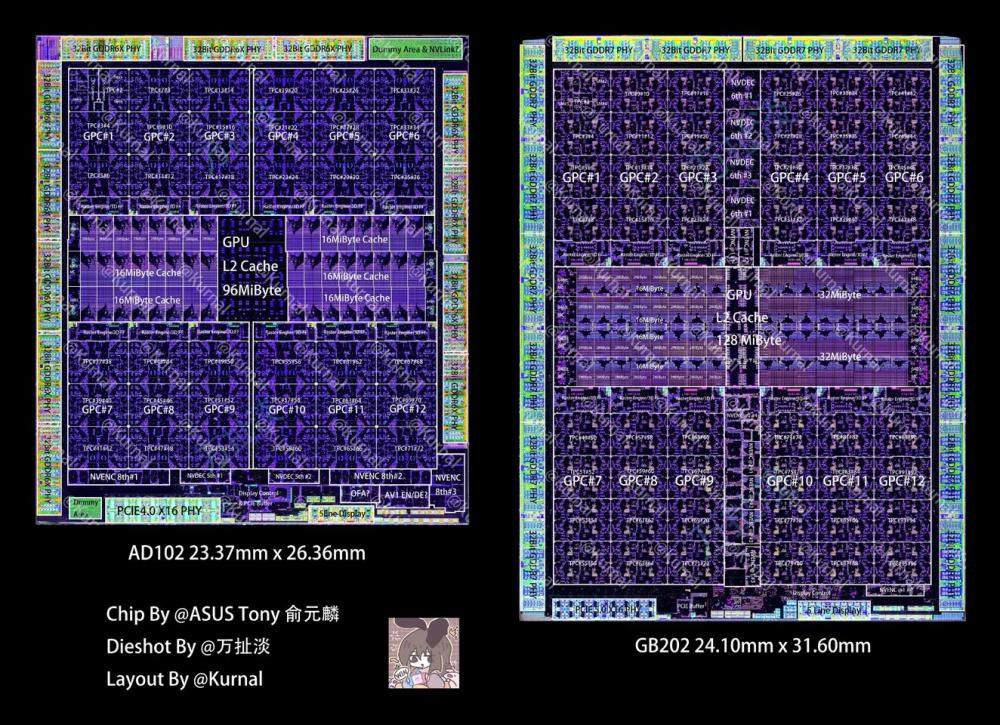

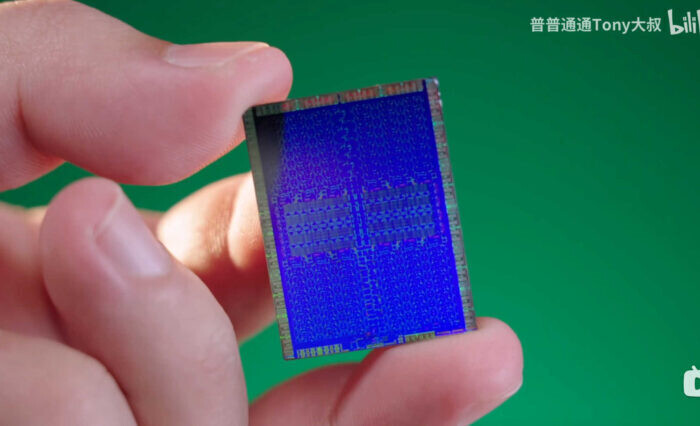

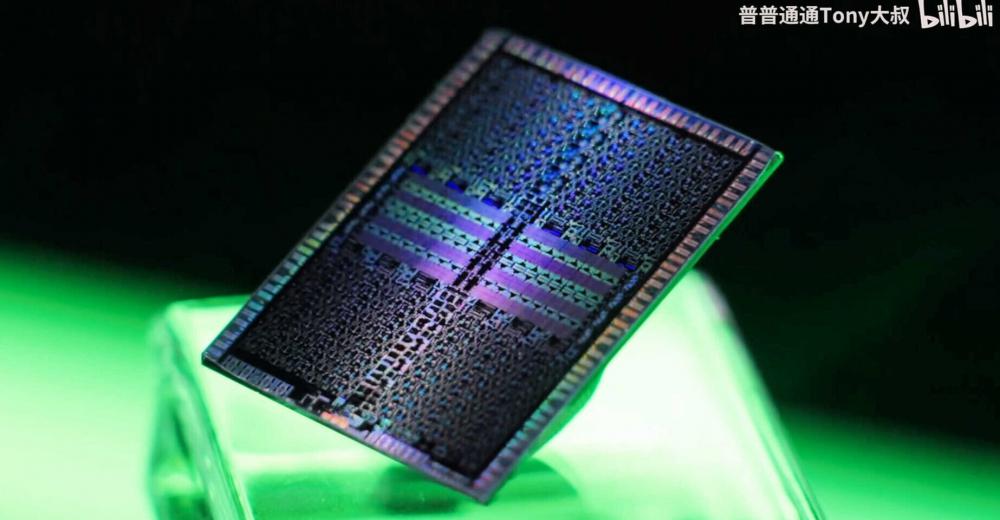

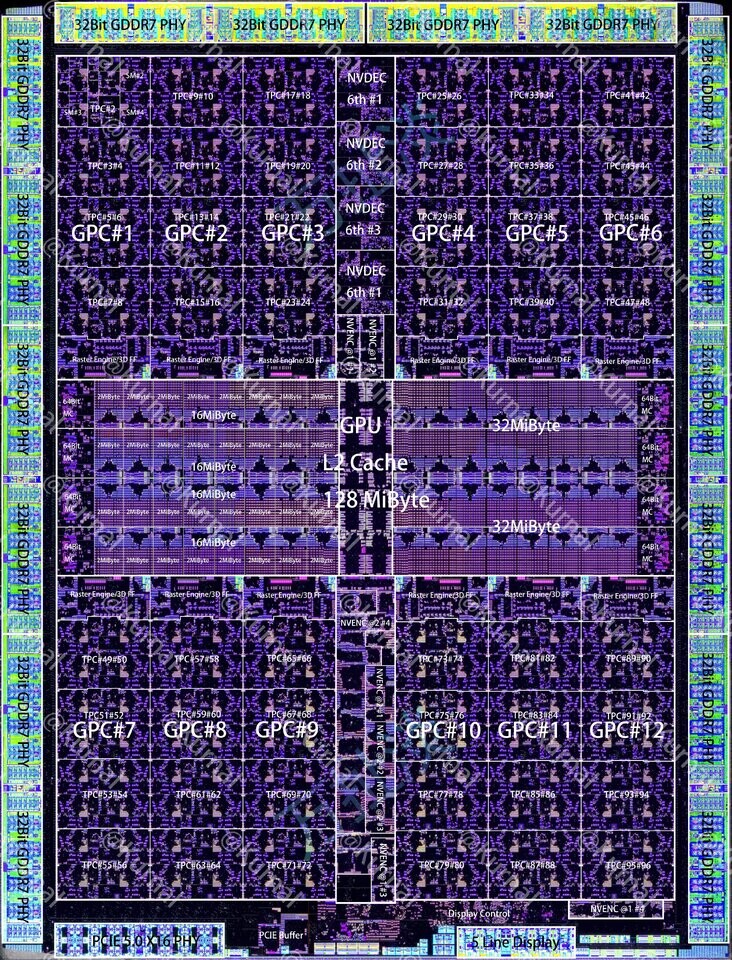

ไดช็อตของ GB202 ของ NVIDIA ซึ่งเป็นซิลิกอนที่ขับเคลื่อน RTX 5090 ได้ปรากฏขึ้นทางออนไลน์ โดยให้ข้อมูลเชิงลึกโดยละเอียดเกี่ยวกับเค้าโครงทางกายภาพของสถาปัตยกรรม "Blackwell" รูปภาพพร้อมคำอธิบายประกอบที่แชร์โดย Kurnal นักวิเคราะห์ฮาร์ดแวร์และจัดทำโดย Tony Yu ผู้จัดการทั่วไปของ ASUS China เปรียบเทียบ GB202 กับรุ่นก่อน AD102 และสรุปส่วนประกอบทางสถาปัตยกรรมที่สำคัญ ส่วนกลางของไดมีแคช L2 ขนาด 128 MB (เปิดใช้งาน 96 MB บน RTX 5090) ล้อมรอบด้วยอินเทอร์เฟซหน่วยความจำ คอนโทรลเลอร์หน่วยความจำ 64 บิตแปดตัวรองรับอินเทอร์เฟซ GDDR7 512 บิต โดยมีอินเทอร์เฟซทางกายภาพวางอยู่ตามขอบด้านบน ด้านซ้าย และด้านขวาของได คลัสเตอร์การประมวลผลกราฟิก (GPC) จำนวนสิบสองคลัสเตอร์ล้อมรอบแคชส่วนกลาง แต่ละ GPC ประกอบด้วยคลัสเตอร์การประมวลผลพื้นผิว (TPC) จำนวนแปดคลัสเตอร์ โดยแต่ละ GPC ประกอบด้วยมัลติโปรเซสเซอร์สตรีมมิ่ง (SM) จำนวน 16 ตัว การกำหนดค่าไดย์แบบสมบูรณ์ช่วยให้มีคอร์ CUDA 24,576 คอร์ จัดเรียงเป็น 128 คอร์ต่อ SM ใน 192 SM โดยที่ RTX 5090 มีคอร์ CUDA "เพียง" 21,760 คอร์ ซึ่งหมายความว่าไดย์ GB202 เต็มรูปแบบนั้นถูกสงวนไว้สำหรับ GPU ของเวิร์กสเตชัน

การออกแบบ SM ประกอบด้วยสไลซ์สี่สไลซ์ที่แชร์แคช L1 ขนาด 128 KB และหน่วยแมปพื้นผิว (TMU) สี่หน่วย สไลซ์ SM แต่ละสไลซ์ประกอบด้วยไฟล์รีจิสเตอร์เฉพาะ แคชคำสั่ง L0 ตัวกำหนดตารางการวาร์ป หน่วยโหลด-สโตร์ และหน่วยฟังก์ชันพิเศษ ใจกลางเค้าโครงของไดย์คือแถบแนวตั้งที่มีส่วนประกอบการประมวลผลสื่อ—หน่วย NVENC และ NVDEC—ทำงานจากบนลงล่าง การใช้งาน RTX 5090 ช่วยให้มีตัวเข้ารหัส NVENC ที่มีอยู่สามในสี่ตัวและตัวถอดรหัส NVDEC สองในสี่ตัว ไดย์ประกอบด้วยบล็อกแรสเตอร์เอ็นจิ้น/FF 3D จำนวนสิบสองบล็อกสำหรับการประมวลผลเรขาคณิต ที่ขอบด้านล่างคืออินเทอร์เฟซ PCIe 5.0 x16 และส่วนประกอบตัวควบคุมการแสดงผล แม้จะมีขนาดใหญ่ แต่ GB202 ก็ยังมีขนาดเล็กกว่าชิป GH100 และ GV100 รุ่นก่อนหน้าของ NVIDIA ซึ่งมีพื้นที่เกิน 814 ตร.มม. ชิป SM แต่ละตัวจะผสานฮาร์ดแวร์เฉพาะทางเข้าด้วยกัน รวมถึงคอร์ Tensor รุ่นที่ 5 และคอร์ RT รุ่นที่ 4 ทำให้ชิปนี้มีคอร์ RT ทั้งหมด 192 คอร์ คอร์ Tensor 768 คอร์ และหน่วยพื้นผิว 768 หน่วย

ที่มา : TechPowerUp

ที่มา : TechPowerUp