Intel ได้สาธิตศักยภาพด้านการแพ็กเกจชิประดับสูง ด้วยผลิตภัณฑ์แบบมัลติชิปเล็ตที่ผสานไทล์บนโหนด 18A/14A เข้ากับเทคโนโลยี Foveros 3D และ EMIB-T

Intel กำลัง “ปรุงของแรง” ด้วยโหนดกระบวนการยุคใหม่ 18A/14A พร้อม Foveros 3D และ EMIB-T

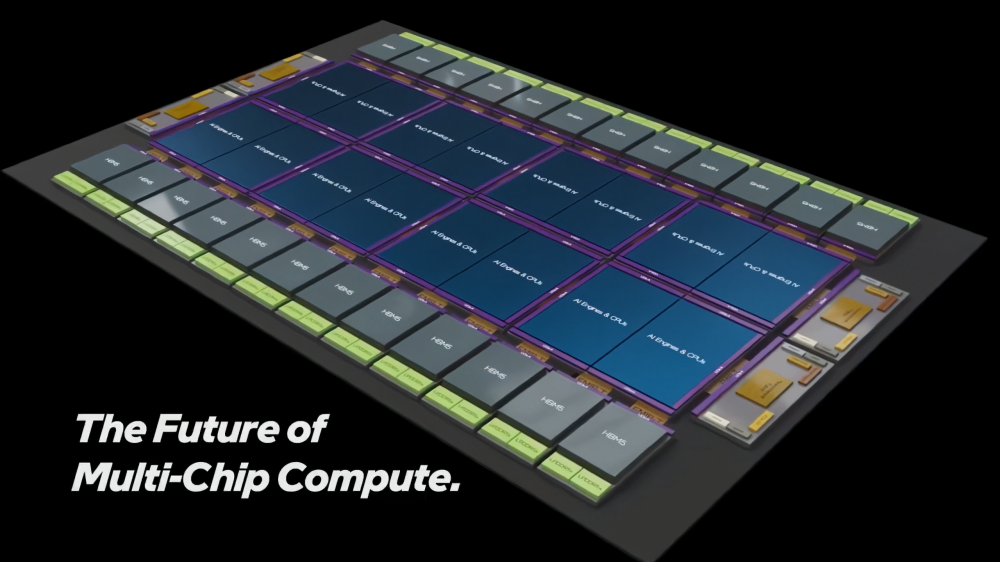

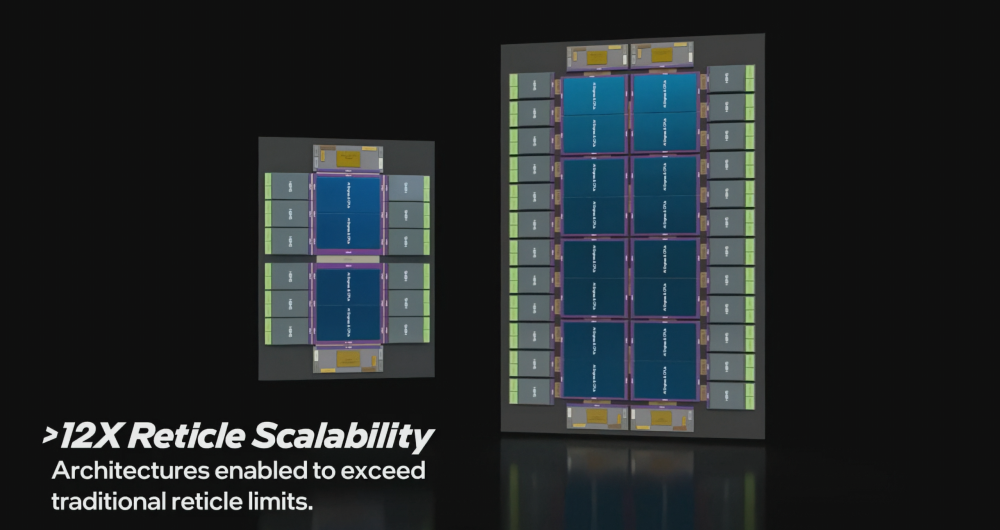

โชว์ดีไซน์เชิงแนวคิดที่ขยายสเกลได้สูงมาก รองรับ Compute Tile สูงสุด 16 ชิ้น, ตำแหน่ง HBM สูงสุด 24 จุด และอีกมากมาย

Intel ไม่ได้กั๊กเทคโนโลยีแพ็กเกจขั้นสูงของตน โดยล่าสุดได้เผยให้เห็นภาพอนาคตสำหรับลูกค้าที่ต้องการใช้โซลูชันของ Intel ในการสร้างชิปรุ่นถัดไป เทคโนโลยีเหล่านี้ถูกวางตำแหน่งให้เป็นมาตรฐานใหม่ของชิปสำหรับงาน HPC, AI, ดาต้าเซ็นเตอร์ และอื่น ๆ อีกทั้งยังเพิ่มแรงกดดันการแข่งขันกับโซลูชัน CoWoS ของ TSMC ซึ่งก่อนหน้านี้ก็ได้เผยแนวทางสเกล 9.5 เรติเคิล บนโหนด A16 พร้อมรองรับ HBM4E มากกว่า 12 ตำแหน่ง (CoWoS-L)

ในภาพตัวอย่างจะเห็นดีไซน์ชิปขนาดใหญ่สองแบบ พร้อมข้อความ “>12X Reticle Scalability” สื่อถึงสถาปัตยกรรมที่ก้าวข้ามข้อจำกัดเรติเคิลแบบดั้งเดิม โดยเทคโนโลยีหลักที่ Intel จะนำมาใช้เพื่อสร้างขุมพลังประมวลผลยุคถัดไป มีดังนี้:

-

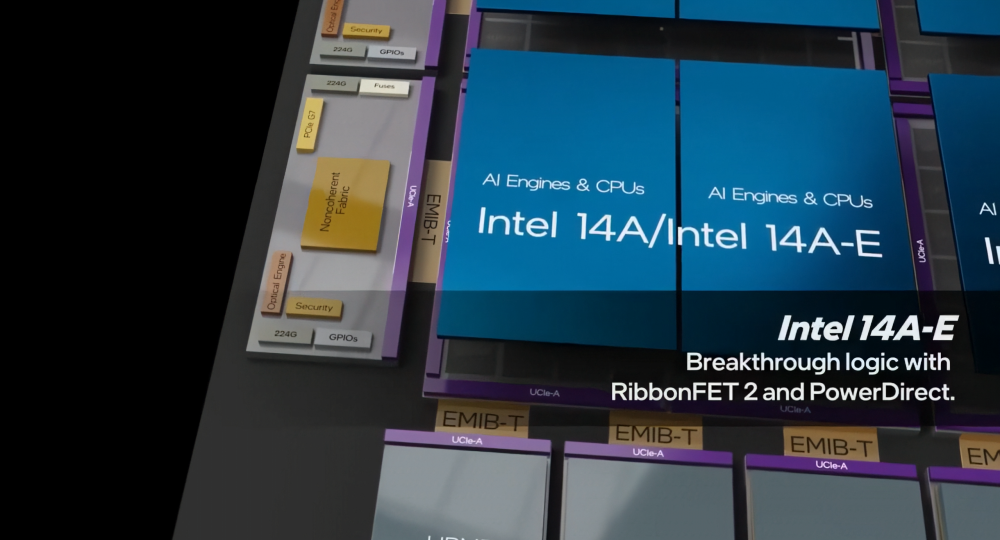

Intel 14A-E: ลอจิกก้าวกระโดดด้วย RibbonFET รุ่นที่ 2 และ PowerDirect

-

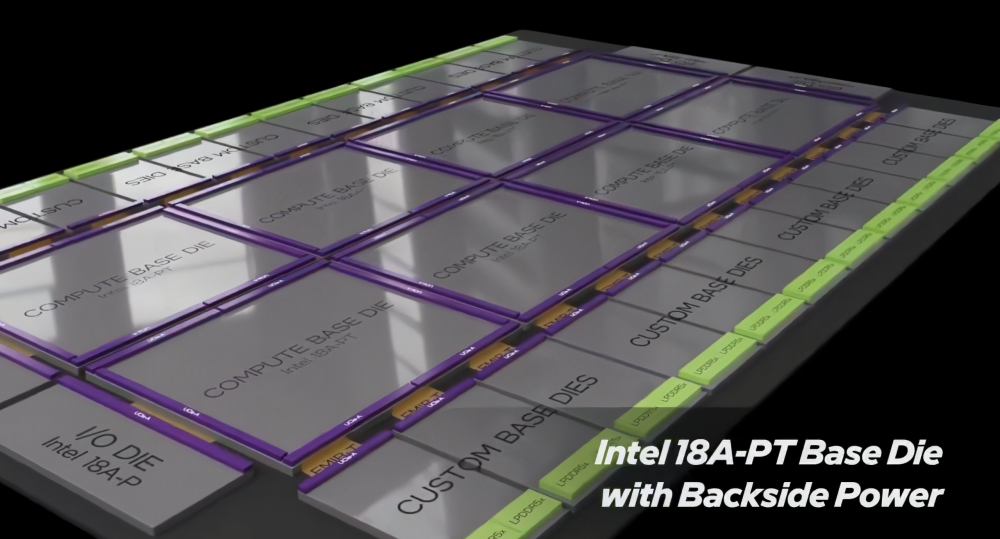

Intel 18A-PT: Base die ตัวแรกที่ใช้ระบบจ่ายไฟด้านหลัง (Backside Power) เพิ่มความหนาแน่นของลอจิกและความเสถียรด้านพลังงาน

-

High-Performance Top Die: ประสิทธิภาพยุคใหม่ พร้อมความหนาแน่นและประสิทธิภาพต่อวัตต์ที่ดีขึ้น (โหนด 14A/14A-E)

-

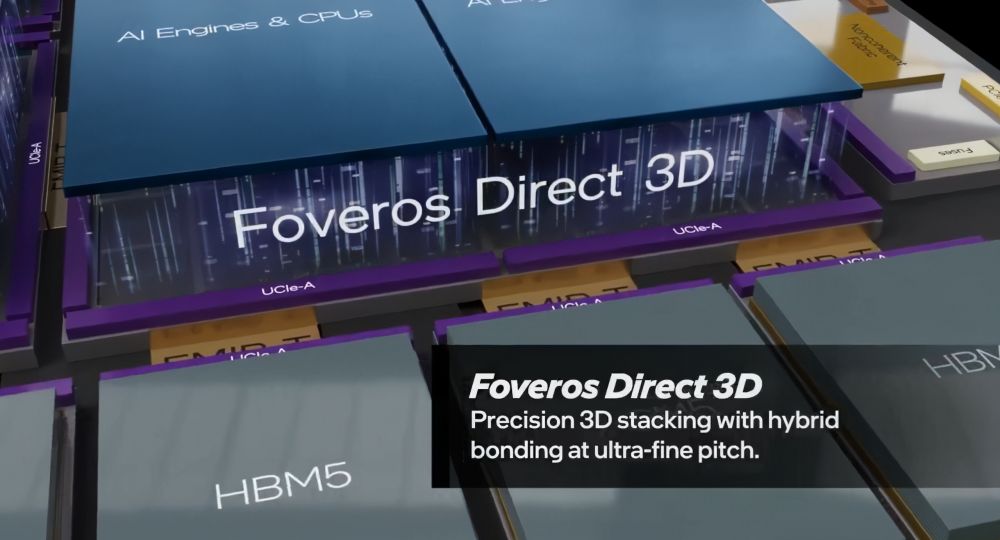

Foveros Direct 3D: การสแต็ก 3 มิติแบบแม่นยำ ด้วย Hybrid Bonding ระยะพิตช์ระดับละเอียดมาก

-

EMIB-T (Embedded Multi-die Interconnect Bridge): EMIB เจเนอเรชันใหม่ เพิ่ม TSV เพื่อแบนด์วิดท์ที่สูงขึ้นและการรวมไทล์ขนาดใหญ่กว่าเดิม

-

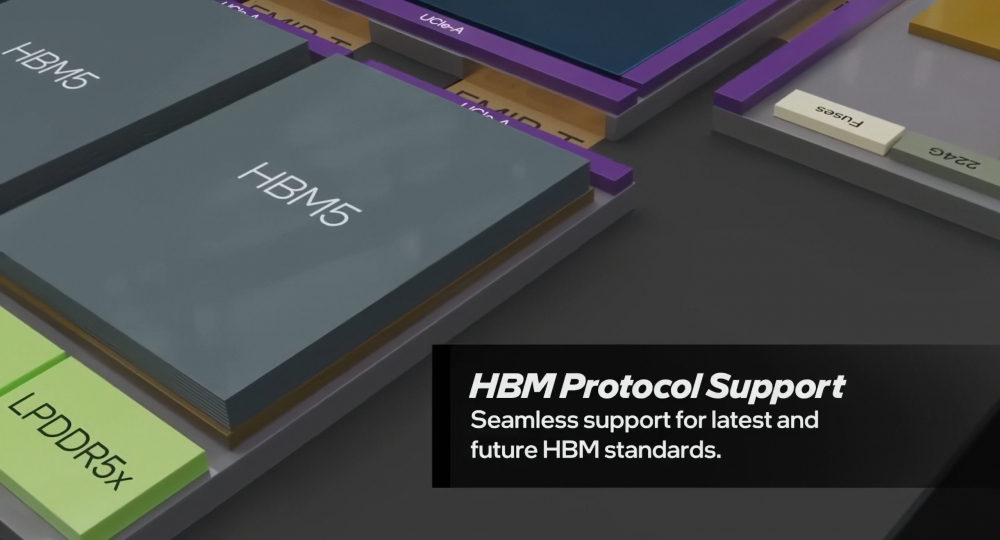

HBM Protocol Support: รองรับมาตรฐาน HBM ปัจจุบันและอนาคตอย่างราบรื่น (HBM4 / HBM5 / HBM-Next)

-

>12x Reticle Scalability: สถาปัตยกรรมที่ออกแบบมาเพื่อขยายเกินขีดจำกัดเรติเคิลเดิม

จากวิดีโอที่ Intel เผยแพร่ มีการโชว์โซลูชันแพ็กเกจขั้นสูง 2 แบบ (เป็นดีไซน์เชิงแนวคิด) แบบแรกมี 4 Compute Tile พร้อม HBM 12 ตำแหน่ง ส่วนแบบที่สองจัดเต็มถึง 16 Compute Tile กับ HBM 24 ตำแหน่ง นอกจากนี้ยังเพิ่มคอนโทรลเลอร์ LPDDR5X เป็นสองเท่า โดยรุ่นใหญ่รองรับได้สูงสุด 48 ตัว

ชิปเหล่านี้ประกอบด้วย Compute Base Die ที่ผลิตบนโหนด 18A-PT ซึ่งทำหน้าที่เป็นที่อยู่ของ SRAM คล้ายแนวคิดของ Clearwater Forest (ที่ใช้ 18A และมี L3 cache รวม 576MB จากโครงสร้าง Base Tile แบบสามชั้น) โดยในอนาคตเมื่อขยับมาใช้ 18A-PT อย่างเต็มรูปแบบ ก็คาดว่าจะเพิ่มประสิทธิภาพและความจุ SRAM ได้มากขึ้นอีก

บน Base Die จะสแต็กด้วย Compute Tile ชั้นบน ซึ่งอาจเป็น AI Engine, CPU หรือ IP อื่น ๆ ผลิตบนโหนด 14A หรือ 14A-E และเชื่อมต่อกันด้วย Foveros 3D ในรูปแบบการสแต็ก 3 มิติ

จากนั้น ชิปเล็ตหลายตัวจะถูกเชื่อมโยงเข้าหากันและต่อกับหน่วยความจำผ่าน EMIB-T โดยแพ็กเกจระดับบนสุดรองรับ HBM ได้ถึง 24 ตำแหน่ง ตั้งแต่ HBM3 / HBM3E ไปจนถึงมาตรฐานอนาคตอย่าง HBM4 / HBM4E หรือ HBM5 และยังสามารถรวม คอนโทรลเลอร์ LPDDR5X ได้สูงสุด 48 ตัว เพื่อเพิ่มความหนาแน่นหน่วยความจำสำหรับงาน AI และดาต้าเซ็นเตอร์อย่างเต็มที่

Intel ระบุด้วยว่ามีแผนสร้างอีโคซิสเต็มที่หลากหลาย และทำงานร่วมกับพาร์ตเนอร์ในอุตสาหกรรมโดยตรง เพื่อเร่งเวลาออกสู่ตลาดและเพิ่มความยืดหยุ่นของซัพพลายเชน

การโชว์แพ็กเกจชิประดับนี้ชัดเจนว่ามุ่งเป้าไปที่ ลูกค้าภายนอก (3rd party) โดยเฉพาะโหนด 14A ซึ่งถูกออกแบบมาเพื่อให้บริการลูกค้าภายนอกเป็นหลัก ขณะที่ 18A จะเน้นใช้กับผลิตภัณฑ์ภายในของ Intel เองก่อน แต่เมื่อผสานกับโซลูชันแพ็กเกจขั้นสูงที่นำเสนอครั้งนี้ ก็สะท้อนว่า Intel กำลังกลับมาเอาจริงในเกมโรงงานผลิต (Fab) อีกครั้ง

สิ่งที่ยังต้องรอดูต่อไปคือ ผลิตภัณฑ์จริงและการยืนยันว่าใครจะได้ใช้ Intel Fab บ้าง แม้จะมีสัญญาณบางอย่างออกมาแล้ว แต่ยังไม่มีอะไรชัดเจน ต้องไม่ลืมว่า Intel เคยอยู่แถวหน้าด้าน Advanced Packaging มานาน ชิประดับตำนานอย่าง Ponte Vecchio คือผลงานเชิงวิศวกรรมที่น่าทึ่ง แต่สุดท้ายเจอปัญหาดีเลย์และยีลด์ จนไม่ประสบความสำเร็จ และหลายโปรเจกต์รวมถึง Falcon Shores ก็ถูกยกเลิกไป

ปัจจุบัน Intel กำลังคัมแบ็กด้วย Jaguar Shores และ GPU สำหรับ AI ที่หลายคนจับตาอย่าง Crescent Island อย่างไรก็ตาม บททดสอบที่แท้จริงคือการคว้าดีลจากลูกค้าภายนอกให้ได้ เพราะอนาคตจำนวนมากของบริษัทกำลังฝากความหวังไว้กับเทคโนโลยี 14A นั่นเอง

ที่มา: Wccftech