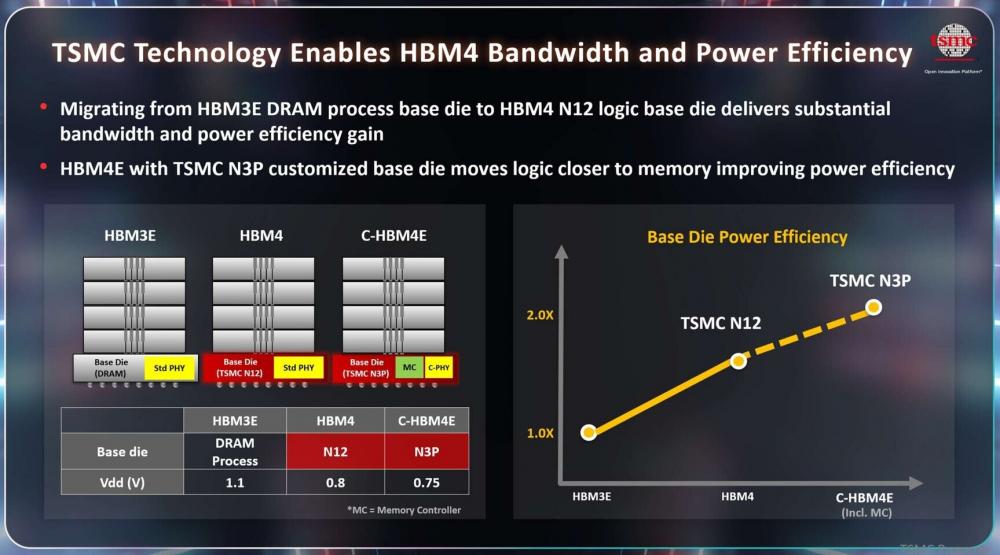

ในงาน Open Innovation Platform Ecosystem Forum ที่อัมสเตอร์ดัมเมื่อสัปดาห์ที่ผ่านมา TSMC ได้เผยข้อมูลเพิ่มเติมเกี่ยวกับเทคโนโลยี HBM4 แบบปรับแต่งพิเศษ ตามรายงานของ HardwareLUXX โดยชิป C-HBM4E logic die แบบคัสตอม ของบริษัทเตรียมย้ายไปผลิตบนโหนด N3P พร้อมลดแรงดันทำงานจาก 0.8 V เหลือ 0.75 V

ตามข้อมูลจากสไลด์นำเสนอของ TSMC การเปลี่ยนโหนดนี้มีเป้าหมายเพื่อเพิ่ม ประสิทธิภาพด้านพลังงาน (power efficiency) ได้ราว 2 เท่า เมื่อเทียบกับกระบวนการผลิต DRAM ปัจจุบัน

แม้แต่ HBM4 รุ่นมาตรฐาน (base die) ก็จะได้รับการอัปเกรดเช่นกัน จากเดิม HBM3E ใช้กระบวนการผลิตแบบ DRAM ปกติ แต่ TSMC มีแผนสร้าง HBM4 base die บนโหนด N12 ซึ่งช่วยลดแรงดันจาก 1.1 V เหลือ 0.8 V ให้ประสิทธิภาพเพิ่มขึ้นประมาณ 1.5 เท่า

สำหรับ C-HBM4E โดยเฉพาะ ไม่ได้ย้ายแค่ตัว base die ไป N3P แต่ยัง รวมคอนโทรลเลอร์หน่วยความจำเข้าไว้ในสแตกโดยตรง จากเดิมที่คอนโทรลเลอร์อยู่บน SoC ของโฮสต์ ส่งผลให้ตัว PHY ต้องออกแบบใหม่ทั้งหมดแบบคัสตอมเต็มรูปแบบ

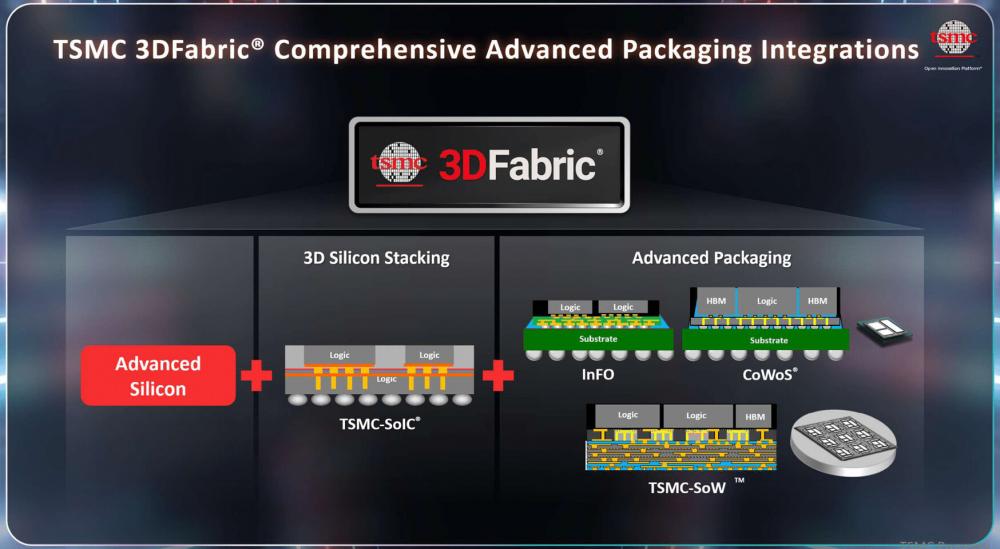

นอกจากนี้ TSMC ยังขยายไลน์เทคโนโลยีแพ็กเกจขั้นสูง โดยอัปเกรดตัวเลือก InFO และ SoW แต่ CoWoS ยังคงเป็นตัวขับเคลื่อนหลักของการเติบโต

หลังจากรองรับขนาด reticle จาก 1.5× ไปสู่ 3.3× พร้อมการติดตั้ง HBM ได้สูงสุด 8 ชิป ตอนนี้เทคโนโลยีมุ่งสู่ CoWoS-L ที่รองรับได้มากถึง 12 กอง (stacks) ของ HBM3E/HBM4 สำหรับชิป AI ปี 2026 และจะมีเวอร์ชันขนาดใหญ่ขึ้นอีกสำหรับรุ่น A16 ในปี 2027

ด้านการผลิต logic die สำหรับ HBM ลูกค้าระดับใหญ่ก็เริ่มเลือกใช้ TSMC มากขึ้น

-

Micron เลือกให้ TSMC ผลิต logic base die สำหรับ HBM4E โดยเตรียมเริ่มผลิตจำนวนมากในปี 2027

-

SK Hynix ก็เตรียมเปิดตัว HBM4E แบบคัสตอมรุ่นแรกครึ่งหลังปีหน้า โดยรายงานจาก Korea Financial Times ระบุว่า SK Hynix จะใช้กระบวนการผลิต 12 nm ของ TSMC สำหรับ HBM ระดับเซิร์ฟเวอร์ทั่วไป ส่วน GPU ระดับสูงของ NVIDIA และ TPU ของ Google จะใช้โหนด 3 nm

เทคโนโลยี HBM4 กำลังจะกลายเป็นก้าวใหญ่ของวงการ AI และ HPC อย่างแท้จริง.

ที่มา: HardwareLUXX