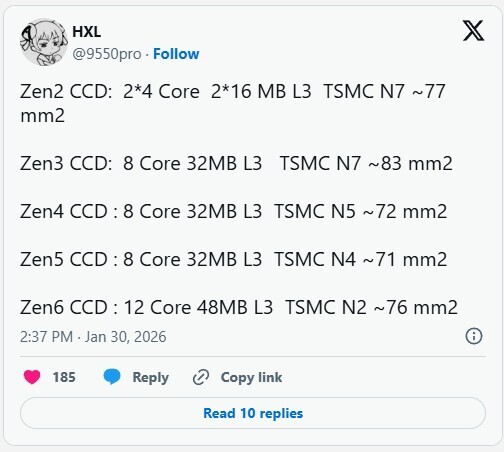

ชิปเล็ต CPU Complex Die (CCD) มาตรฐานของ AMD ที่ใช้สถาปัตยกรรมรุ่นถัดไป “Zen 6” เตรียมก้าวกระโดดครั้งใหญ่ ด้วยการเพิ่มจำนวนคอร์ซีพียูขึ้นถึง 50% นี่ถือเป็นครั้งแรกที่ AMD เพิ่มจำนวนคอร์ใน CCD ที่ใช้คอร์ขนาดเต็ม ซึ่งสามารถรักษาความเร็วสัญญาณนาฬิกาสูงได้ ต่างจากก่อนหน้านี้ที่เน้น CCD คอร์จำนวนมากแต่เป็นคอร์ขนาดกะทัดรัดและมีเพดานความเร็วต่ำกว่า

คาดว่า CCD ของ “Zen 6” จะมีขนาดไดใกล้เคียงกับ “Zen 5” รุ่นปัจจุบัน โดยมีข่าวลือว่าขนาดอยู่ที่ราว 76 ตารางมิลลิเมตร เพิ่มขึ้นเล็กน้อยจาก 71 ตารางมิลลิเมตรของ “Zen 5”

สำหรับโครงสร้างภายใน “Zen 6” CCD จะบรรจุคอร์ซีพียู 12 คอร์ อยู่ภายใต้ CPU Core Complex (CCX) เดียว และคอร์ทั้ง 12 จะใช้แคช L3 ร่วมกันขนาด 48MB ซึ่งทั้งจำนวนคอร์และขนาดแคช L3 เพิ่มขึ้น 50% เมื่อเทียบกับ “Zen 5”

AMD จะผลิต “Zen 6” CCD บนกระบวนการ TSMC N2 (2 นาโนเมตร แบบ nanosheet) ที่ให้ความหนาแน่นของทรานซิสเตอร์สูงขึ้นอย่างมาก เมื่อเทียบกับ TSMC N4P (4 นาโนเมตร แบบ FinFET) ที่ใช้กับ “Zen 5” ในปัจจุบัน

ขณะเดียวกัน เมื่อมองไปที่ฝั่ง Intel ซึ่งกำลังปรับทิศทางมาเน้นแคชระดับ last-level ขนาดใหญ่ในซีพียูเดสก์ท็อประดับพรีเมียม Core Ultra 400 “Nova Lake-S” AMD เองก็คาดว่าจะใส่ความสามารถรองรับ 3D V-Cache ให้กับ “Zen 6” CCD เต็มรูปแบบ ส่งผลให้ซีพียู X3D รุ่นถัดไปอาจมีแคช L3 สูงสุดถึง 144MB ต่อหนึ่ง CCD และรวมได้สูงสุดถึง 288MB บนแพลตฟอร์มเดสก์ท็อปซ็อกเก็ต AM5

ที่มา: VideoCardz