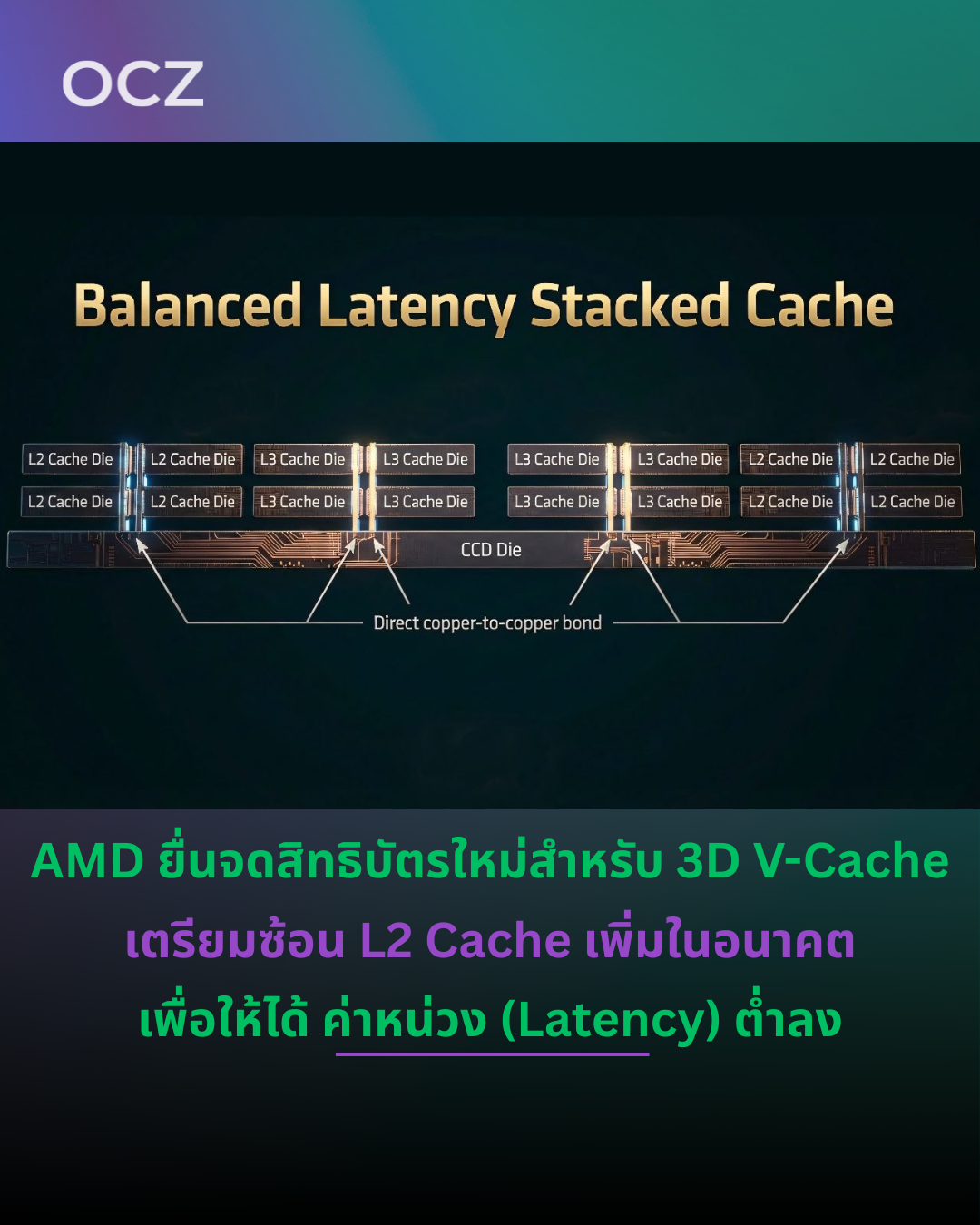

สื่อต่างประเทศรายงานว่า AMD ได้ยื่นจดสิทธิบัตรใหม่เกี่ยวกับเทคโนโลยี 3D V-Cache เมื่อไม่นานมานี้ โดยใช้หมายเลขคำขอ US20260003794A1 ภายใต้ชื่อ “Balanced Latency Stacked Cache” ซึ่งระบุว่าในอนาคต 3D V-Cache จะไม่ได้ซ้อนแค่ L3 Cache เพื่อเพิ่มความจุเท่านั้น แต่จะซ้อน L2 Cache ไปพร้อมกันด้วย เพื่อช่วยลดค่าหน่วง (Latency) ให้ต่ำลงอีกขั้น

ตามรายงานแนวคิด Balanced Latency Stacked Cache ยังคงใช้หลักการเดียวกับ 3D V-Cache รุ่นปัจจุบัน คือเชื่อมต่อ Cache Die เข้ากับฐานซิลิคอนและชุดประมวลผลด้วย TSV (Through-Silicon Vias) แต่ความแตกต่างสำคัญคือ Die ของ L2 Cache จะถูกวางซ้อนในตำแหน่งที่ใกล้กับแกน CPU มากขึ้น

เอกสารสิทธิบัตรระบุว่าโครงสร้างใหม่นี้ไม่เพียงช่วยลดค่า Latency ในการเข้าถึงแคชแบบซ้อนชั้นเท่านั้น แต่ยังช่วย ลดการใช้พลังงาน ได้อีกด้วย

เมื่อเทียบกับแคชแบบแบน (Planar Cache) ที่สร้างอยู่บน CCD เดียวกัน Balanced Latency Stacked Cache จะวางจุดเชื่อมต่อและสายสัญญาณไว้ในตำแหน่ง “กึ่งกลาง” ของระบบแคชแบบซ้อนชั้น ช่วยหลีกเลี่ยงการต้องลากสัญญาณไกลข้ามพื้นที่แคชเหมือนในดีไซน์แบบเดิม ซึ่งมักต้องเพิ่มขั้นตอนสายสัญญาณ (Wire / Pipe Stages) เพื่อส่งข้อมูลไปยังจุด I/O ที่อยู่ไกลกว่า

AMD ยกตัวอย่างว่า L2 Cache แบบแบนขนาด 1MB มีค่า Latency โดยทั่วไปประมาณ 14 Clock Cycles แต่ L2 Cache แบบซ้อนชั้นขนาด 2MB สามารถลดเหลือเพียง 12 Clock Cycles เนื่องจากระยะทางของสายสัญญาณสั้นลง นั่นหมายความว่า L2 Cache แบบซ้อนชั้นไม่เพียงให้ความจุสูงขึ้น แต่ยังมี Latency ใกล้เคียงหรือดีกว่าแบบดั้งเดิมด้วย

เนื่องจากคำสั่งเข้าถึงข้อมูลใช้เวลาน้อยลง L2 Cache แบบซ้อนชั้นจึงไม่จำเป็นต้องคงสถานะทำงาน (Active) เป็นเวลานาน และสามารถเข้าสู่โหมดว่าง (Idle) ได้เร็วขึ้น ส่งผลดีต่อ ประสิทธิภาพการใช้พลังงานของ CPU

นอกจากนี้ สายสัญญาณที่สั้นลงยังช่วยลดค่าความจุไฟฟ้า (Capacitance) และลดการใช้พลังงาน เพราะสัญญาณต้องวิ่งเพียงประมาณครึ่งหนึ่งของระยะเดิม ทำให้ภาระของสัญญาณ (Signal Loading) ลดลง และเกิดความร้อนน้อยลงตามไปด้วย

อย่างไรก็ตาม ในตอนนี้เทคโนโลยี Balanced Latency Stacked Cache ยังอยู่ในขั้นตอนของสิทธิบัตรเท่านั้น กว่าจะได้เห็นนำมาใช้งานจริงบนผลิตภัณฑ์เชิงพาณิชย์ คงต้องใช้เวลาอีกพอสมควร

ที่มา: HKEPC