หลังจาก TSMC ประกาศชัดว่าจะเริ่มกระบวนการผลิตขนาด 7 นาโนเมตรในปีหน้า Samsung เองก็ไมนิ่งเฉย ประกาศอัพเดทโร้ดแมปครั้งใหญ่เช่นกัน โดยเผยว่าจะเริ่มกระบวนการผลิต 5 นาโนเมตรในปีหน้า และ 3 นาโนเมตรในอนาคตด้วยกระบวนการผลิต MBCFET (ข้างในคือ GAAFET)

ในงาน Samsung Foundry Forum ที่เมือง Santa Clara แคลิฟอร์เนียทางบริษัทเผยว่าได้เริ่มส่ง Design Kits ของ 3 นาโนเมตรให้กับผู้ผลิตชิปต่างๆ เมื่อเดือนที่ผ่านมา โดยเทคนิคนี้เป็นผลงานจากความร่วมมือกับ IBM เพื่อทำให้ GAAFET (Gate-all-around-FET) ใช้งานได้จริง แต่มีการเปลี่ยนแปลงจากของเดิมที่ IBM ออกแบบไว้เล็กน้อยและใช้ชื่อใหม่ว่า MBCFET ทำให้กระแสไฟไหลได้มากขึ้น ชดเชยพื้นที่นำไฟฟ้า nanowire และ nanosheet ในระบบ GAAFET

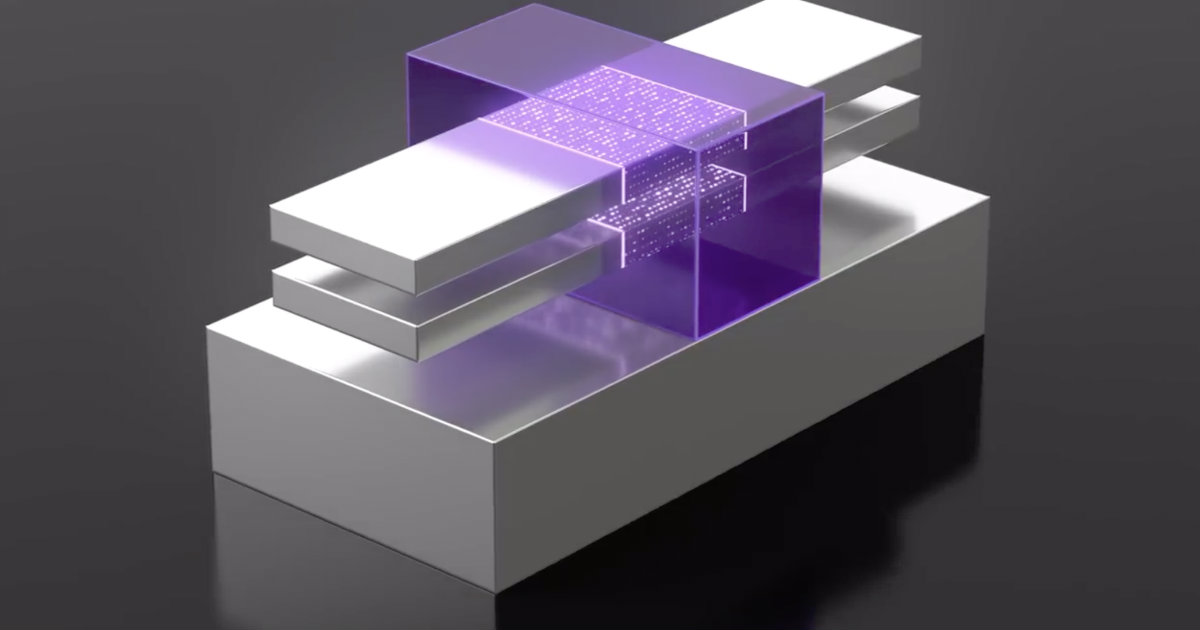

เทคนิค GAAFET นี้จะทำให้ Gate ล้อมรอบช่องทางเดินกระแสไฟฟ้า ทำให้ลดแรงดันไฟที่ต้องใช้ลงให้ต่ำกว่า 0.75 แอมแปร์ และสามารถทำงานร่วมกับชิปที่ออกแบบ FinFET มาได้ไม่ยาก และไม่ต้องใช้อุปกรณ์ใหม่ๆ เพื่อกระบวนการผลิตดังกล่าว

การผลิตแบบ 3 นาโนเมตร MBCFET จะลดอัตราการบริโภคพลังงาน และไฟฟ้าลงได้ 30% และ 45% ตามลดำดับ เมื่อเทียบกับ 7 นาโนเมตรแล้วถือว่าดีกว่าเดิมพอสมควร ส่วนในแง่ของประสิทธิภาพการทำงานแล้วดีขึ้น 40% เลยทีเดียว

นอกจาก 3 นาโนเมตรที่เป็นของน่าตื่นตาตื่นใจแล้ว Samsung เผยว่ามีแผนจะเร่งกระบวนการผลิตให้สามารถผลิต 4,5 และ 6 นาโนเมตรได้ด้วย โดยปลายปีนี้จะเริ่มต้นผลิต 6 นาโนเมตร และคาดว่าในชว่วงนั้นงานวิจัยเพื่อผลิต 4 นาโนเมตรน่าจะเสร็จสิ้นแล้ว ส่วน 5 นาโนเมตรจะเริ่มผลิตในปี 2020 ช่วงเดียวกันกับ TSMC

ที่มา - TSMC