ฝ่ากำแพงหน่วยความจำ: พื้นฐานของ HBM และการมาถึงของ HBM4 ในยุค AI

เมื่อ ยุคของ HBM4 กำลังใกล้เข้ามา และ SK hynix กับ Micron เตรียมเพิ่มกำลังการผลิตตั้งแต่ปลายปี 2025 ถึง 2026 ถือเป็นช่วงเวลาที่เหมาะสมในการทำความเข้าใจว่า HBM (High Bandwidth Memory) ถูกสร้างขึ้นอย่างไร มีข้อดีและเทคโนโลยีอะไรบ้าง และทำไมความซับซ้อนในการผลิตถึงทำให้มีราคาสูง

ภายใน HBM: โครงสร้างและข้อดีหลัก

เมื่อโมเดล AI มีความซับซ้อนมากขึ้น ทั้งการฝึกสอนขนาดใหญ่และการประมวลผลแบบเรียลไทม์ ต้องการหน่วยความจำที่ตอบโจทย์ 3 ด้านหลัก ๆ คือ ความจุ, ความเร็ว และประสิทธิภาพ

-

SRAM เร็วมาก แต่ความจุน้อย

-

DRAM แบบดั้งเดิม มีความจุมาก แต่แบนด์วิดท์ต่ำ

-

HBM จึงเป็นทางออกกลาง ให้ทั้งความจุและความเร็วที่สมดุล

HBM ทำได้ด้วย สถาปัตยกรรมแบบซ้อน (Stacked Architecture): มี DRAM หลายชั้นวางอยู่บน Logic Die (ฐาน) และเชื่อมต่อกันด้วย Interconnects นับพันเส้น ทั้งหมดนี้เชื่อมกับ xPU ผ่าน Silicon Interposer บน substrate ของแพ็กเกจ มักใช้งานร่วมกับ GPU เช่น ของ NVIDIA

ข้อดีหลักของ HBM

-

ประหยัดพลังงาน: การเชื่อมต่อใกล้ xPU ทำให้เส้นทางข้อมูลสั้น ลดการใช้พลังงาน

-

แบนด์วิดท์มหาศาล:

-

HBM4 ใช้พลังงานน้อยกว่า DDR4 40–50% แต่ได้แบนด์วิดท์เท่ากัน

-

DDR4 สูงสุดประมาณ 25.6 GB/s แต่ HBM4 stack เดียว >1 TB/s

-

ฝ่ากำแพงหน่วยความจำ: ทำไม HBM จึงขับเคลื่อนยุค AI

ในยุค AI สร้างโมเดลขนาดใหญ่ เช่น ChatGPT ต้องใช้ GPU หลายหมื่นตัวพร้อมกัน แต่แม้กำลัง GPU จะเพิ่มขึ้น 60,000 เท่าใน 20 ปีที่ผ่านมา แบนด์วิดท์ของ DRAM เพิ่มเพียง 100 เท่า เกิดสิ่งที่เรียกว่า Memory Wall คือ GPU แม้แรง แต่ถ้าหน่วยความจำส่งข้อมูลช้า ก็เป็นคอขวด

HBM ใช้สถาปัตยกรรมซ้อนในแนวตั้งเหมือน ตึกสูง (Skyscraper) แต่ละ DRAM die หนาประมาณ 30–50 µm เชื่อมกับ Logic Die ผ่าน TSV (Through-Silicon Vias) และ Microbumps ก่อนเชื่อมกับ GPU ผ่าน Silicon Interposer

การออกแบบนี้ช่วยให้ ถ่ายโอนข้อมูลผ่านหลายพันช่องทางพร้อมกัน แบนด์วิดท์สูงกว่าหน่วยความจำ DDR ทั่วไปมาก

ราคาของนวัตกรรม: ความท้าทายทางวิศวกรรมของ HBM

การสร้าง “ตึกสูง” แบบนี้มีค่าใช้จ่ายสูงมาก

-

HBM3e เปิดตัวพร้อม Premium 20%

-

HBM4 ด้วยความซับซ้อนมากขึ้น คาดว่าจะสูงกว่า 30%

สาเหตุราคาสูงมาจาก:

-

การออกแบบชิปที่ซับซ้อนขึ้น เพิ่ม I/O Count

-

การเปลี่ยนไปใช้ Logic-based Base Die เพื่อเพิ่มประสิทธิภาพ

ความซับซ้อนในการซ้อนชั้น (Stacking) เป็นอุปสรรคหลัก การเพิ่มชั้นเป็น 12 หรือ 16 ชั้น ทำให้ Yield ของ TSV เป็นคอขวด

แนวทางแก้ไขของผู้ผลิต:

-

SK hynix ใช้ MR-MUF (Mass Reflow Molded Underfill)

-

Samsung / Micron ใช้ TC-NCF (Thermal Compression with Non-Conductive Film)

MR-MUF ทำงานเหมือน “สองขั้นตอนในหนึ่ง”: เชื่อมชิปและใส่วัสดุป้องกันในขั้นตอนเดียว ทำให้เร็วขึ้น แข็งแรงขึ้น และลดปัญหาในการผลิต

-

การ Reflow: ทำให้ bumps เชื่อมชิปซ้อนกัน

-

การ Underfill: เติมช่องว่างด้วยวัสดุป้องกัน เพิ่มความทนทานและระบายความร้อน

MR-MUF ให้ ความนำความร้อนมากกว่า NCF 2 เท่า ส่งผลต่อความเร็วในการผลิตและ yield

Hybrid Bonding เชื่อมชิปโดยตรงไม่มี bumps ทำให้ stack บางลง เพิ่มชั้นได้มากขึ้น ลดการสูญเสียสัญญาณ และ yield ดีขึ้น สำหรับ HBM4 16hi บางผู้ผลิตพิจารณาใช้ Hybrid Bonding และยืนยันใช้ใน HBM5 20hi

HBM4 Base Die: ทำไมผู้ผลิตต้องพึ่ง Foundry

การซ้อน DRAM เป็นเพียงจุดเริ่มต้น อีกความท้าทายคือ สร้างบนฐานที่แม่นยำสูง (Logic Die)

-

ต้องรองรับ 2,000 จุดเชื่อมต่อ (I/O 1,024–2,048)

-

ระยะห่างเพียง 6–9 µm (~100 เท่าบางกว่าผมคน)

ผู้ผลิต DRAM แบบดั้งเดิมเผชิญกับงานที่ยากเกินไป จึงต้องพึ่ง Foundry เช่น TSMC

-

TSMC N12FFC+: สร้าง 12-stack (48GB) หรือ 16-stack (64GB) แบนด์วิดท์ >2 TB/s

-

TSMC N5: ระยะ 6–9 µm รองรับ Direct Bonding สร้าง stack บน Logic Die โดยตรง

HBM: เกม Oligopoly

ผู้ผลิต HBM4 แข่งกันเพื่อให้ NVIDIA ยืนยันการใช้งาน

-

SK hynix: 59% ของการส่งมอบ 2025

-

Samsung / Micron: 20% ต่อราย

GPU ตัวท็อปที่ใช้ HBM4:

-

NVIDIA Rubin GPU

-

AMD MI400 series

HBM4 Spec:

-

DRAM die หนา 30–50 µm

-

Stack 4, 8, หรือ 12 dies

-

ความหนาแพ็กเกจ HBM4 12-high และ 16-high: 775 µm (เพิ่มจาก HBM3 720 µm)

-

I/O เพิ่มจาก 1,024 → 2,048

-

Data rate >8 Gbps เหมือน HBM3e แต่แบนด์วิดท์เพิ่ม 2 เท่า

การทำงานร่วมกับ Logic Die ทำให้ Foundry อย่าง TSMC มีบทบาทสำคัญมากขึ้น เช่นร่วมกับ SK hynix (HBM4) และ Micron (HBM4E) ทำให้สงคราม HBM4 น่าติดตามและแข่งขันสูง

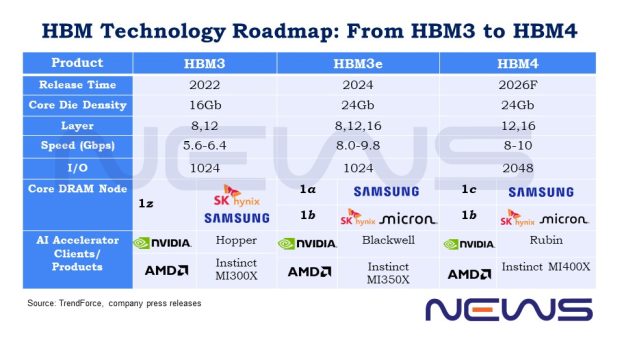

ที่มา: TrendForce